# **IIIILASER 128 SERIES**

# APPLE\*IIc/IIe COMPATIBLE COMPUTER

# Technical Reference Manual

# The following message is applicable to FCC Class B version units only :

Note: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15, of FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures :

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/television technician for help.

You may find the following booklet prepared by the Federal Communications Commission helpful: "How to Identify and Resolve Radio-TV Interference Problems" This booklet is available from the U.S. Government Printing Office, Washington, DC20402, Stock No. 004-000-00345-4.

To ensure that the use of this product does not contribute to interference, it is necessary to use shielded I/O cables.

# TABLE OF CONTENTS

| 1. | Intr | oductio  | n         |                                         | 1-1  |

|----|------|----------|-----------|-----------------------------------------|------|

|    | 1.1  | Organ    | isation o | f manual                                | 1-1  |

|    | 1.2  | Other    | sources   | of information                          | 1-3  |

| 2. | Cent | tral Pro | cessing l | U <b>nit</b>                            | 2-1  |

| 3. | Mem  | lory org | anisatio  | a                                       | 3-1  |

|    | 3.1  | System   | n address | s map                                   | 3-1  |

|    | 3.2  | ROM      |           |                                         | 3-2  |

|    |      | 3.2.1    | The BA    | SIC interpreter                         | 3-3  |

|    | .w.  | 3.2.2    | The sys   | tem monitor                             | 3-3  |

|    |      | 3.2.3    | I/O fir   | mwares                                  | 3-4  |

|    |      |          | 3.2.3.1   | I/O firmwares map                       | 3-4  |

|    |      |          | 3.2.3.2   | I/O firmware                            |      |

|    |      |          |           | control                                 | 3-5  |

|    | 3.3  | RAM      |           |                                         | 3-7  |

|    |      | 3.3.1    | RAM n     | nemory usage                            | 3-8  |

|    |      | 3.3.2    | High-ba   | ank RAM memory                          | 3-11 |

|    |      |          | 3.3.2.1   | High-bank RAM                           |      |

|    |      |          |           | switches                                |      |

|    |      | 3.3.3    |           | nk RAM memory                           | 3-19 |

|    |      |          | 3.3.3.1   | National Condition of the second second |      |

|    |      |          |           | the stack                               | 3-19 |

|    |      |          | 3.3.3.2   | DESCONTRACTOR D. C. DESCHARTS           |      |

|    |      |          |           | memory                                  | 3-20 |

|    |      |          | 3.3.3.3   |                                         |      |

|    |      |          |           | memory                                  |      |

|    | 3.4  | Hardy    | vare pag  | e                                       | 3-37 |

| 4. | Keyb | oard a  | nd speak                                                                                                        | er                    | 4-1  |

|----|------|---------|-----------------------------------------------------------------------------------------------------------------|-----------------------|------|

|    | 4.1  | Keybo   | oard                                                                                                            |                       | 4-1  |

|    |      | 4.1.1   | Accessi                                                                                                         | ng the keyboard       | 4-6  |

|    |      | 4.1.2   | Special                                                                                                         | function keys and     |      |

|    |      |         | -                                                                                                               | s                     | 4-8  |

|    | 4.2  | Speak   | er                                                                                                              |                       | 4-10 |

| 5. | The  | video d | lisplay                                                                                                         |                       | 5-1  |

|    | 5.1  | Text    | modes                                                                                                           |                       | 5-4  |

|    |      | 5.1.1   | Charact                                                                                                         | ter sets              | 5-5  |

|    |      | 5.1.2   | Memory                                                                                                          | mapping               | 5-8  |

|    |      |         | a set of the | 40-column text        |      |

|    |      |         | 5.1.2.2                                                                                                         | 80-column text        | 5-10 |

|    | 5.2  | Graph   |                                                                                                                 | 28                    |      |

|    |      | 5.2.1   |                                                                                                                 | solution graphics     |      |

|    |      | 5.2.2   |                                                                                                                 | low-resolution        |      |

|    |      |         |                                                                                                                 | S                     | 5-15 |

|    |      | 5.2.3   |                                                                                                                 | solution graphics     |      |

|    |      |         | 0                                                                                                               | Monochrome high-      |      |

|    |      |         | 2536756/                                                                                                        | resolution graphics   | 5-19 |

|    |      |         | 5.2.3.2                                                                                                         | Color high-resolution |      |

|    |      |         | - 11 - 51 - 51 - 51 - 51 - 51 - 51 - 51                                                                         | graphics              | 5-22 |

|    |      | 5.2.4   | Double                                                                                                          | -high-resolution      |      |

|    |      | 0.2.1   |                                                                                                                 | S                     | 5-25 |

|    |      |         | 5.2.4.1                                                                                                         | Monochrome double-    |      |

|    |      |         | 0.2.111                                                                                                         | resolution graphics   | 5-25 |

|    |      |         | 5242                                                                                                            | Color double-high-    |      |

|    |      |         |                                                                                                                 | resolution graphics   | 5-28 |

|    | 5.3  | Mixed   | granhie                                                                                                         | s/text modes          |      |

|    | 5.4  |         |                                                                                                                 | play page             |      |

|    | 5.4  | Secon   | uary uns                                                                                                        | bin ) babe            | 0 00 |

| 6. | Disk | input/   | output                           | 6-1  |

|----|------|----------|----------------------------------|------|

|    | 6.1  | Basic    | operating principles of disk     |      |

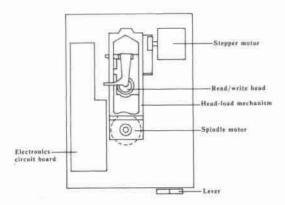

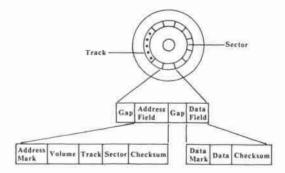

|    |      | drives   |                                  | 6-2  |

|    | 6.2  | Unive    | rsal Disk controller             | 6-6  |

|    | 6.3  | Interf   | acing with non-intelligent 5.25" |      |

|    |      | disk d   | rives                            | 6-8  |

|    |      | 6.3.1    | Moving the read/write head       | 6-9  |

|    |      | 6.3.2    | Reading data from the disk       |      |

|    |      |          | drive                            |      |

|    |      | 6.3.3    | Writing data to the diskette     | 6-17 |

|    | 6.4  | Interf   | acing with non-intelligent 3.5"  |      |

|    |      | disk d   | lrives                           | 6-20 |

|    |      | 6.4.1    | Reading dive status              | 6-22 |

|    |      | 6.4.2    | Sending commands to the disk     |      |

|    |      |          | drive                            |      |

|    |      | 6.4.3    | Reading disk data                | 6-27 |

|    |      | 6.4.4    | Writing data to the disk         |      |

|    |      |          | drive                            | 6-29 |

|    | 6.5  | Interf   | acing with intelligent disk      |      |

|    |      | drives   |                                  | 6-31 |

| 7. | Expa | nsion    | RAM                              | 7-1  |

|    |      |          |                                  |      |

|    | 7.1  | Acces    | sing the expansion RAM           | 7-1  |

|    | 7.2  | Appli    | cations of the expansion         |      |

|    |      | RAM      |                                  | 7-4  |

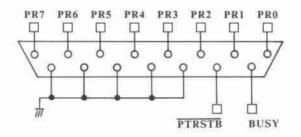

| 8. | Para | llel pri | nter port and serial ports       | 8-1  |

|    | 8.1  | Parall   | el printer port                  | 8-1  |

|    | 8.2  |          | ports                            |      |

|    | 0.2  | Serial   | ports                            | 0-0  |

| 9.  | Game  | e port                               | 9-1   |

|-----|-------|--------------------------------------|-------|

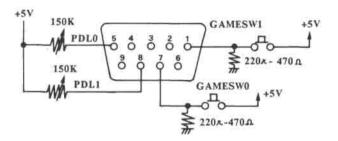

|     | 9.1   | Switch and analog inputs             | 9-2   |

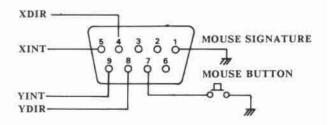

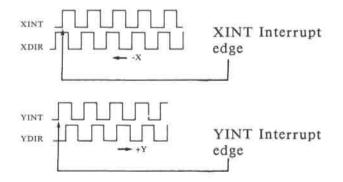

|     | 9.2   | Mouse input                          | 9-5   |

| 10. | Syste | em firmware                          | 10-1  |

|     | 10.1  | System kernél                        | 10-1  |

|     |       | 10.1.1 Power-up and CONTROL-         |       |

|     |       | RESET                                | 10-2  |

|     |       | 10.1.2 Interrupt and BRK             |       |

|     |       | handling                             | 10-5  |

|     |       | 10.1.3 Miscellaneous routines        | 10-10 |

|     |       | 10.1.4 The system monitor            | 10-22 |

|     | 10.2  | Input/Output routines                | 10-26 |

|     |       | 10.2.1 Port 0 : 40-column display    |       |

|     |       | routines                             | 10-32 |

|     |       | 10.2.2 Port 3: 80-column display     |       |

|     |       | routines                             | 10-35 |

|     |       | 10.2.3 Port 1 : Printer routines     | 10-38 |

|     |       | 10.2.4 Port 2 : Serial communication |       |

|     |       | routines                             | 10-43 |

|     |       |                                      |       |

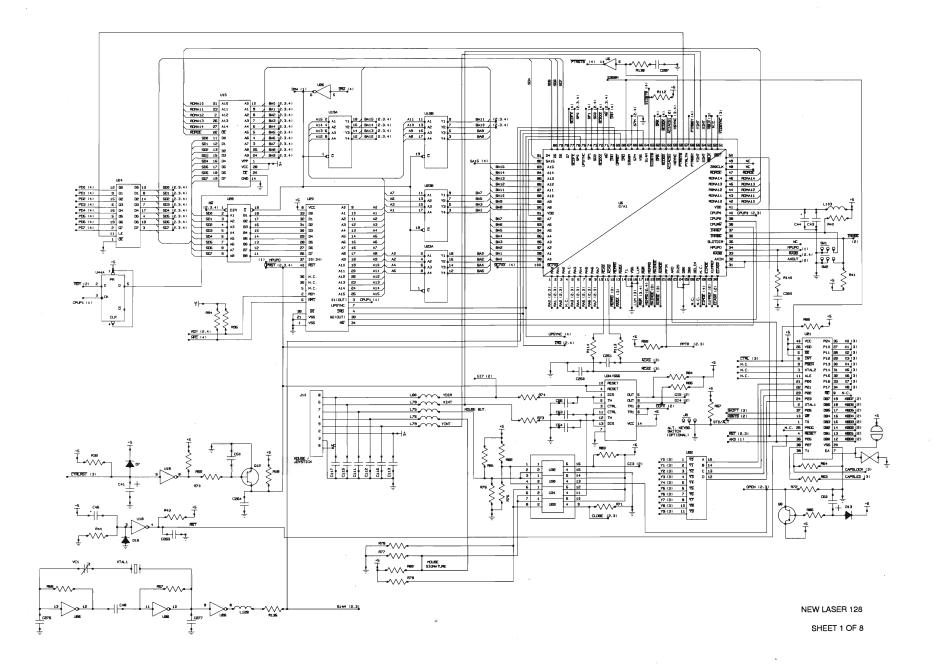

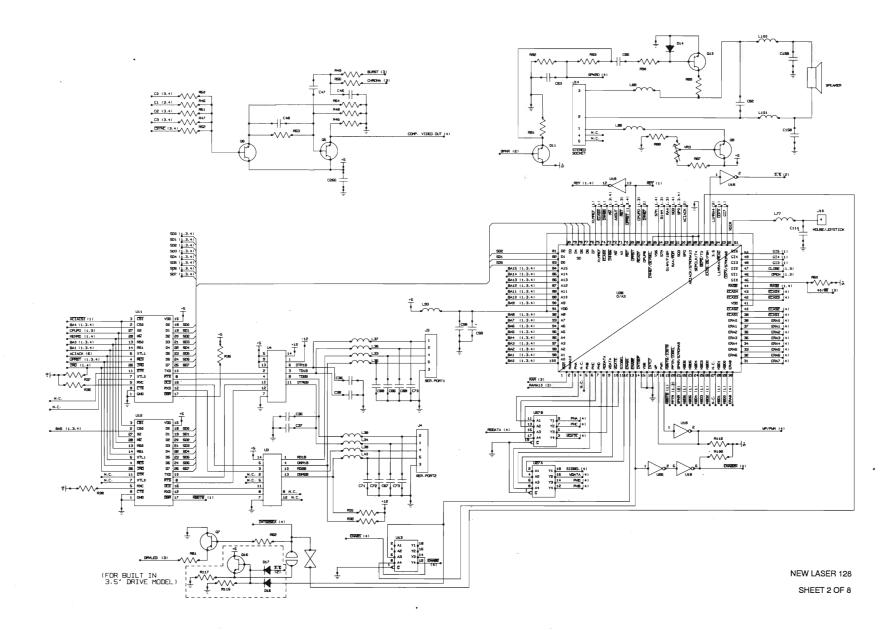

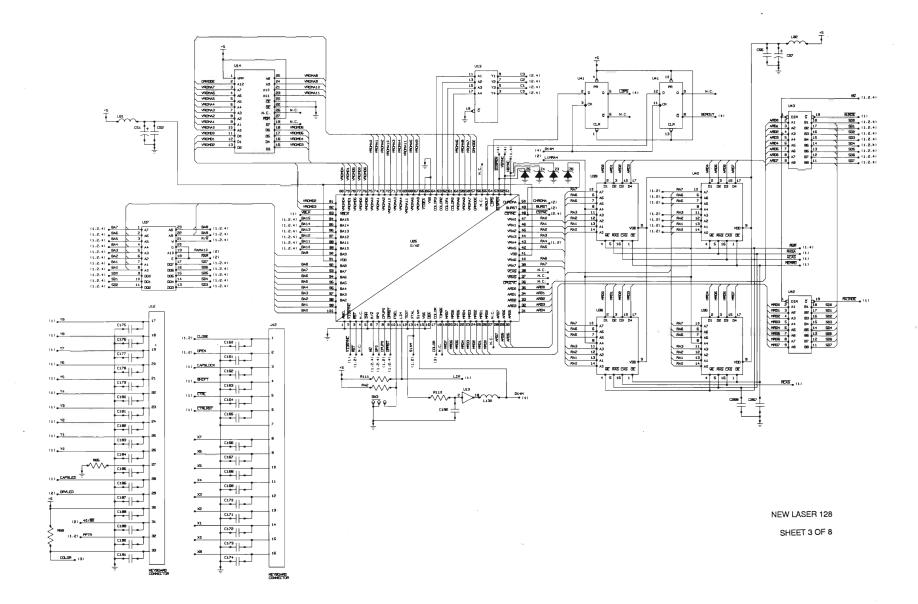

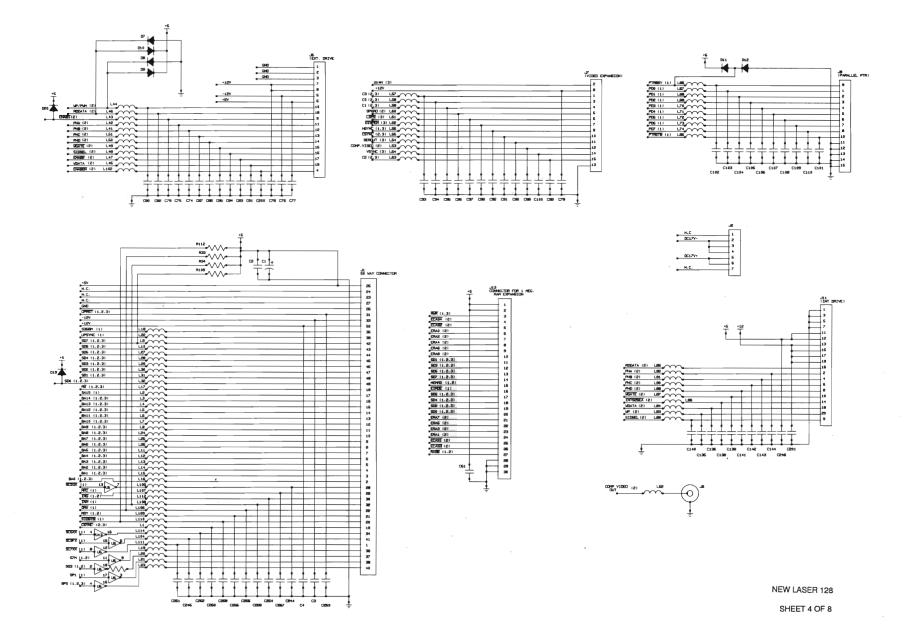

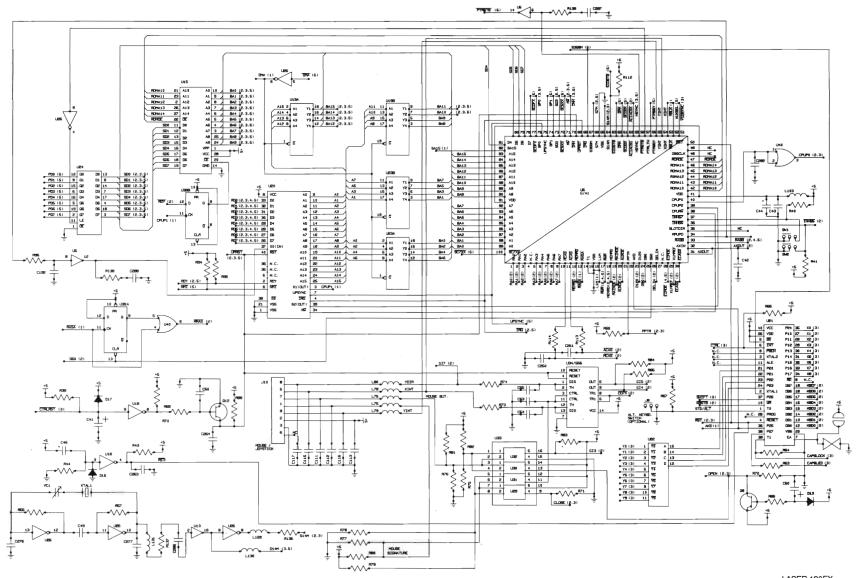

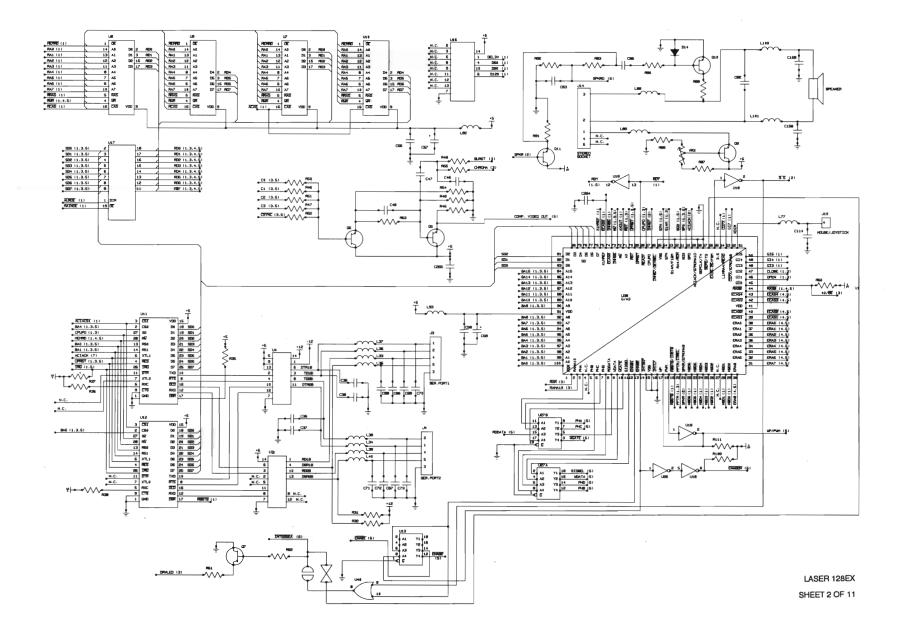

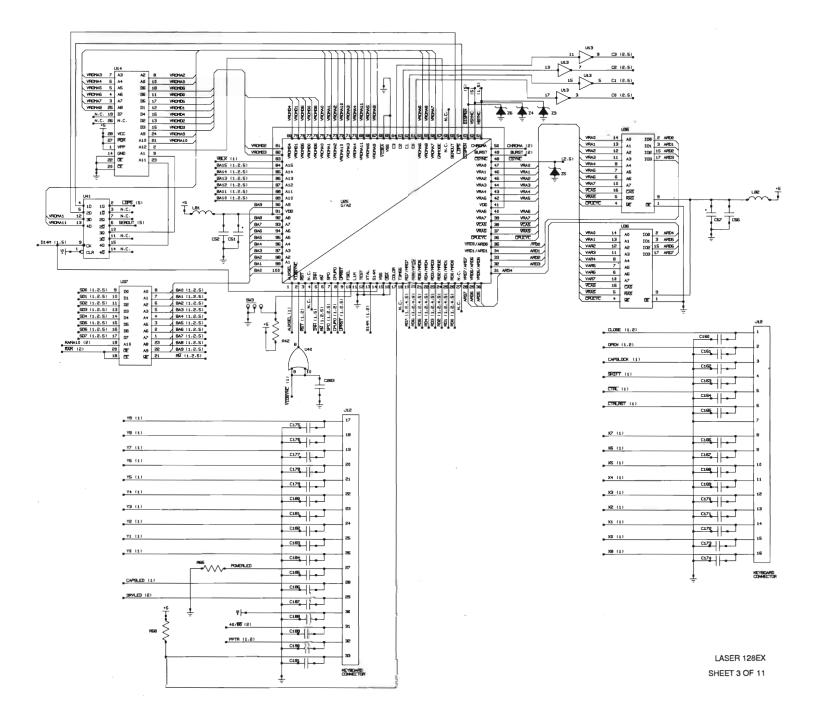

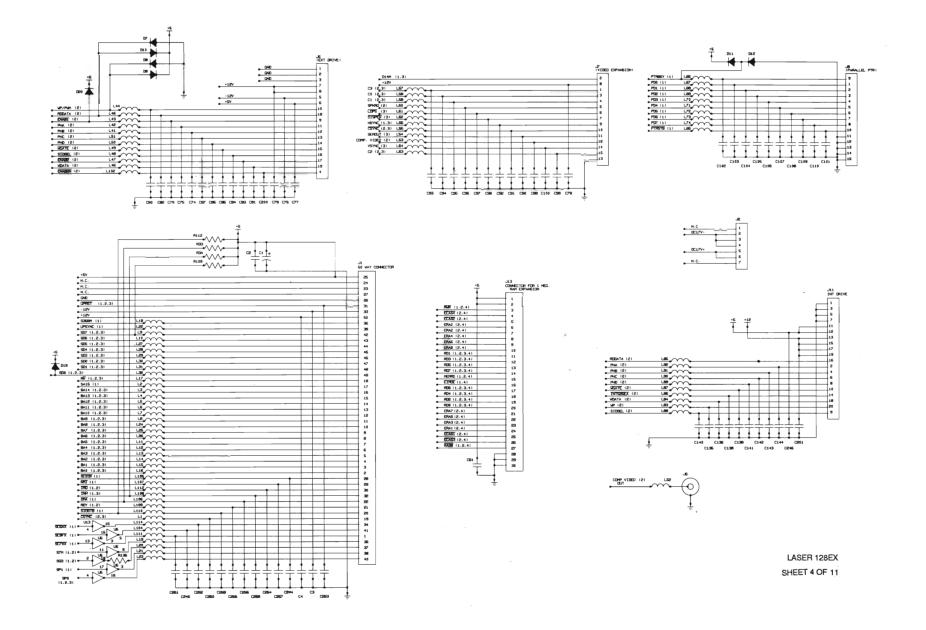

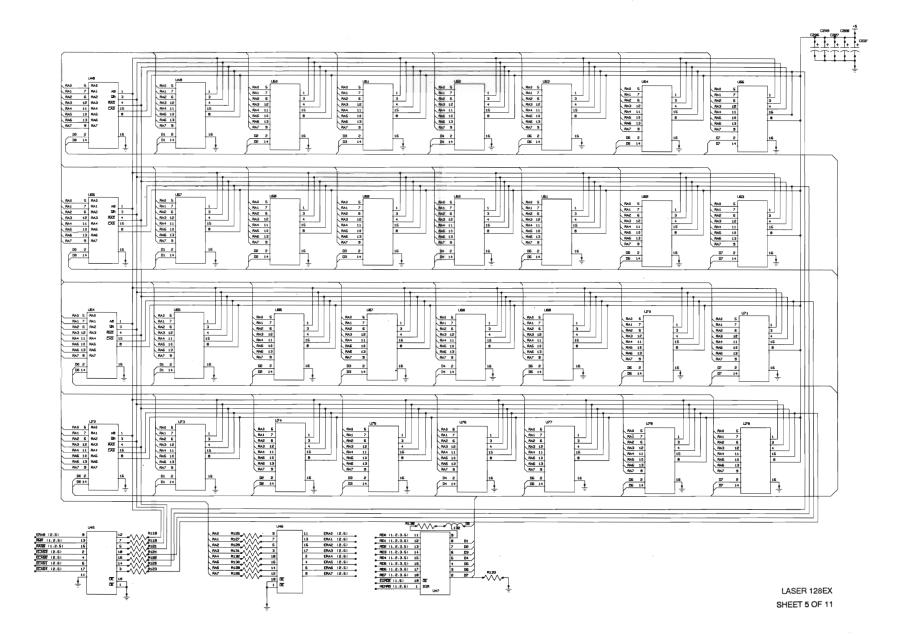

| 11. | Hard  | lware implementation                 | 11-1  |

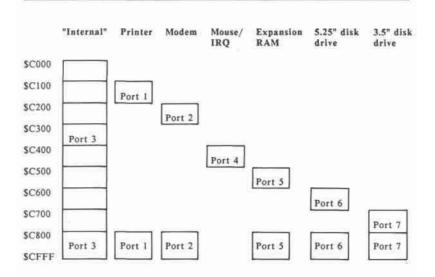

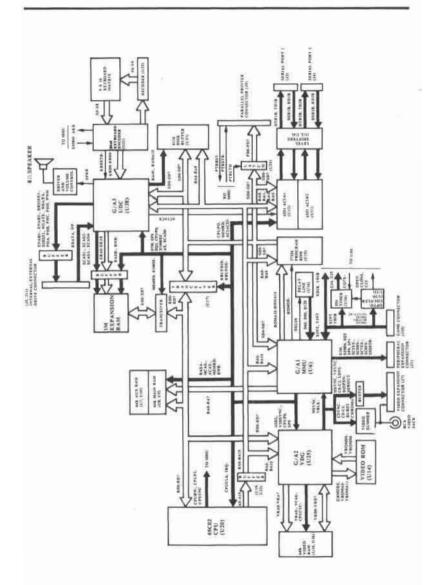

|     | 11.1  | System overview                      | 11-1  |

|     | 11.2  |                                      |       |

|     | 11.3  | CPU and system buses                 | 11-10 |

|     |       | D DOM DOM                            | 11 10 |

| 11.4 | Program ROM control      | 11-13 |

|------|--------------------------|-------|

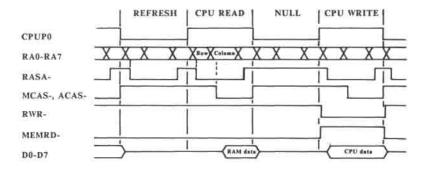

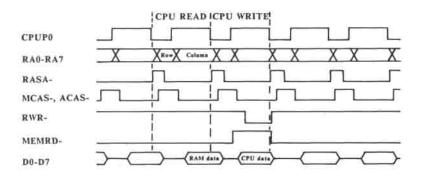

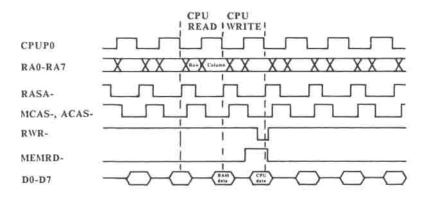

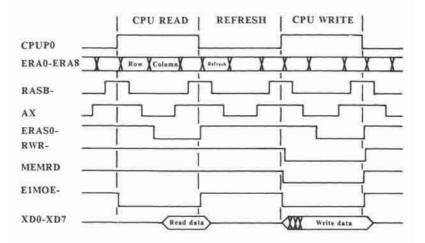

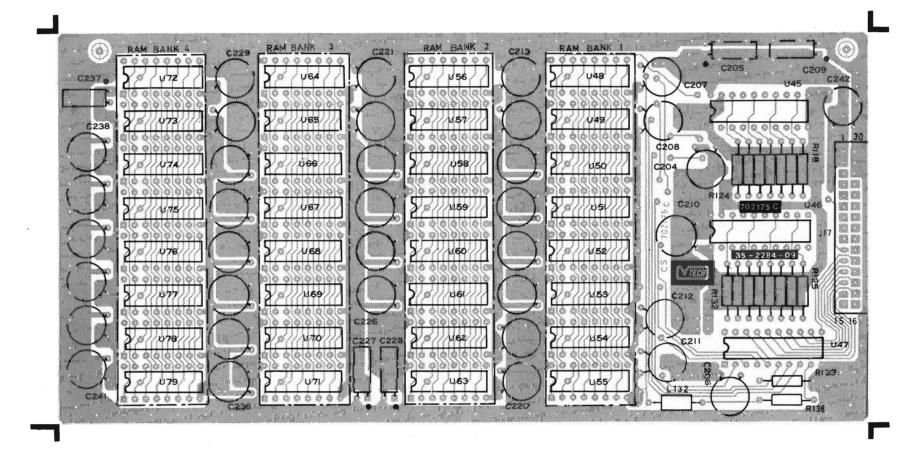

| 11.5 | System RAM control       | 11-15 |

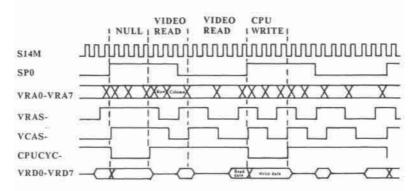

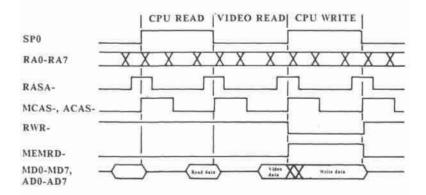

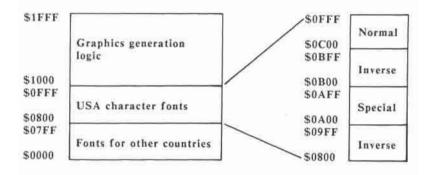

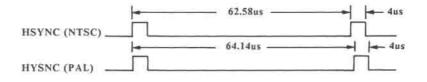

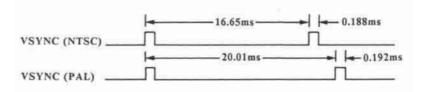

| 11.6 | Video display generation | 11-20 |

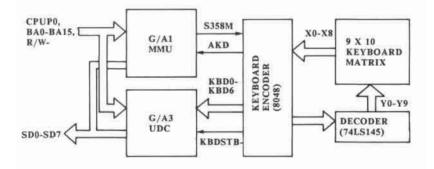

| 11.7 | Keyboard control         | 11-38 |

#### TABLE OF CONTENTS

| 11.8  | Speaker control             | 11-41 |

|-------|-----------------------------|-------|

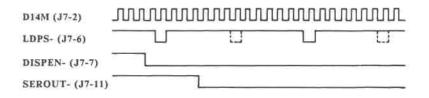

| 11.9  | Disk drive control          | 11-41 |

| 11.10 | Expansion RAM control       | 11-46 |

| 11.11 | Serial port control         | 11-50 |

| 11.12 | Parallel printer control    | 11-52 |

| 11.13 | Joystick and paddle control | 11-54 |

| 11-14 | Mouse control               | 11-56 |

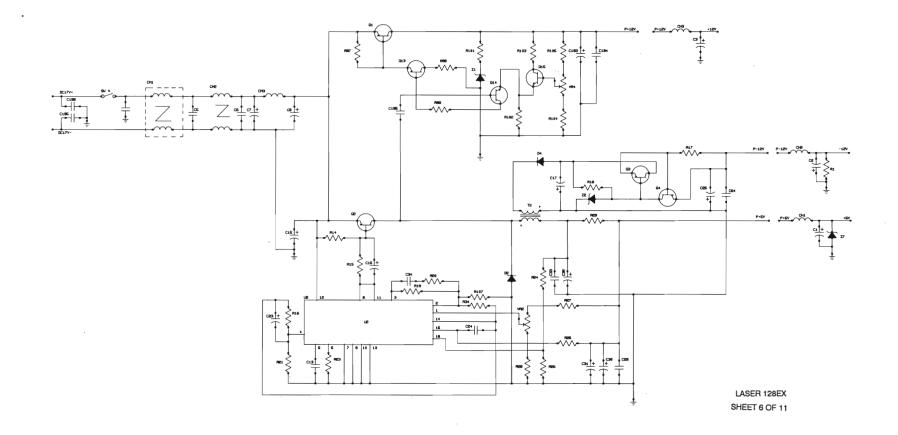

| 11-15 | Power supply                | 11-59 |

### APPENDIX

| A. | CPU  | speed control in "LASER 128 EX" A-1 |

|----|------|-------------------------------------|

| B. | Keyl | board layouts and key codes B-1     |

| C. | 65C0 | 2 programming specification C-1     |

| D. | Serv | ice information D-1                 |

|    | D.1  | Trouble shoot guide D-1             |

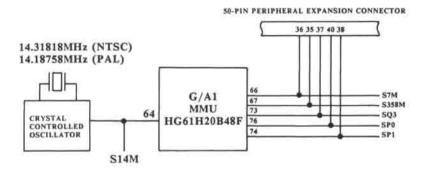

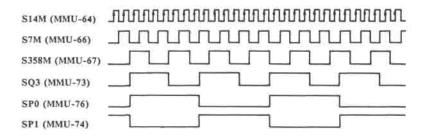

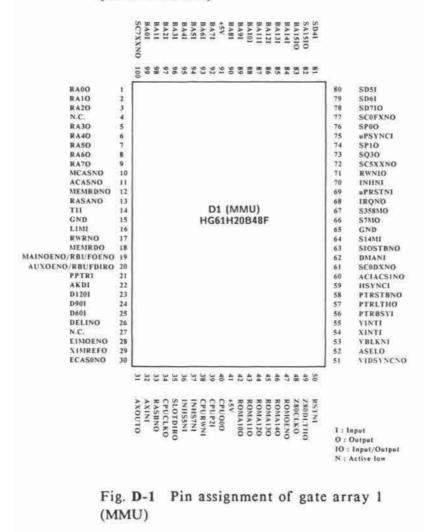

|    | D.2  | Gate array pin assignment D-21      |

|    |      | D.2.1 Gate array 1 : MMU D-21       |

|    |      | D.2.2 Gate array 2 : VDG D-37       |

|    |      | D.2.3 Gate array 3 : UDC D-53       |

#### TABLE OF CONTENTS

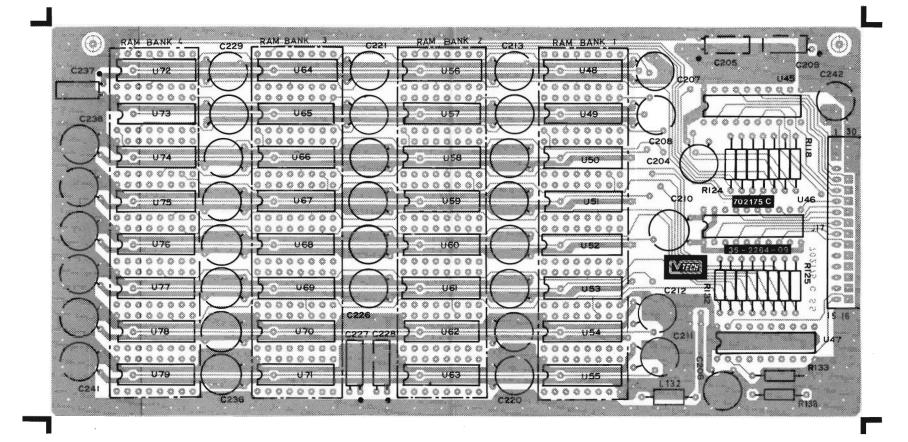

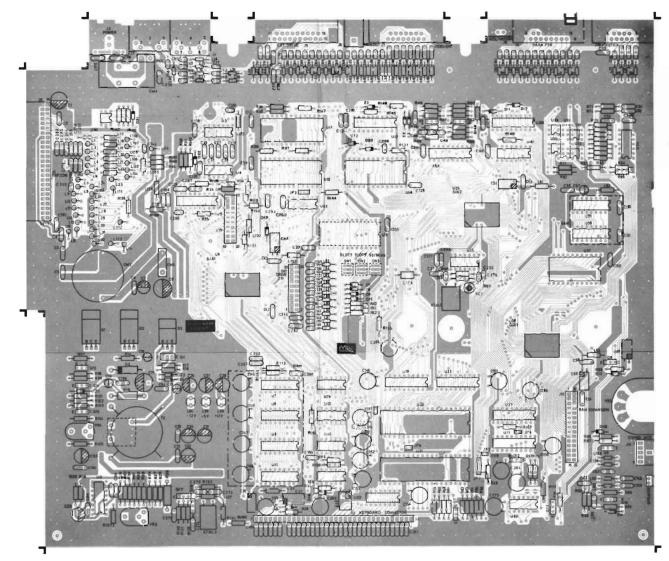

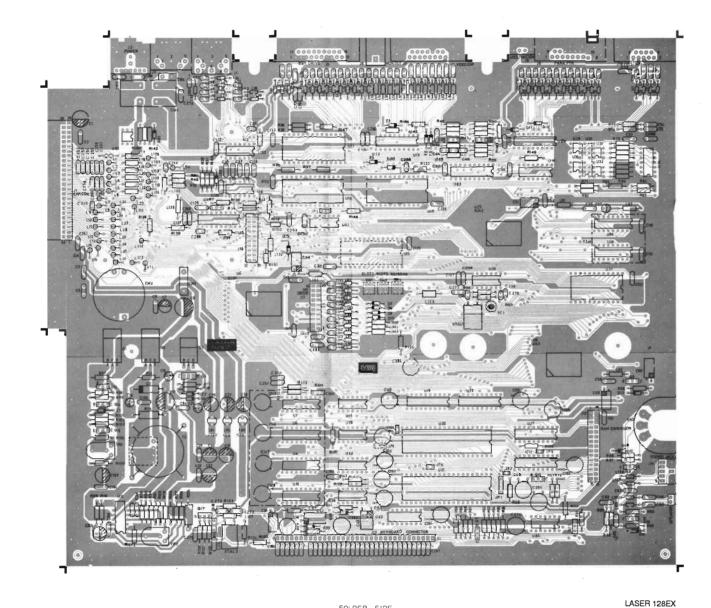

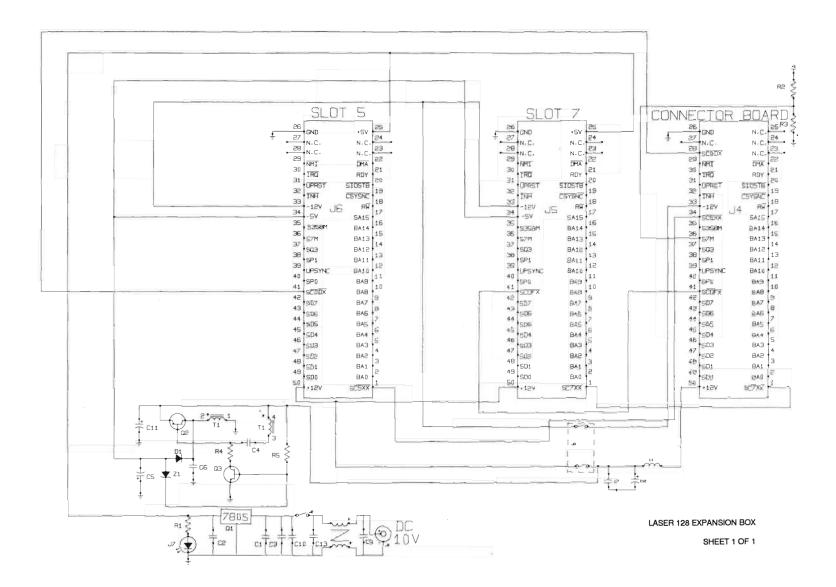

| D.3 | Parts  | lists                     | D-66  |

|-----|--------|---------------------------|-------|

|     | D.3.1  | LASER 128                 | D-66  |

|     | D.3.2  | LASER 128EX               | D-74  |

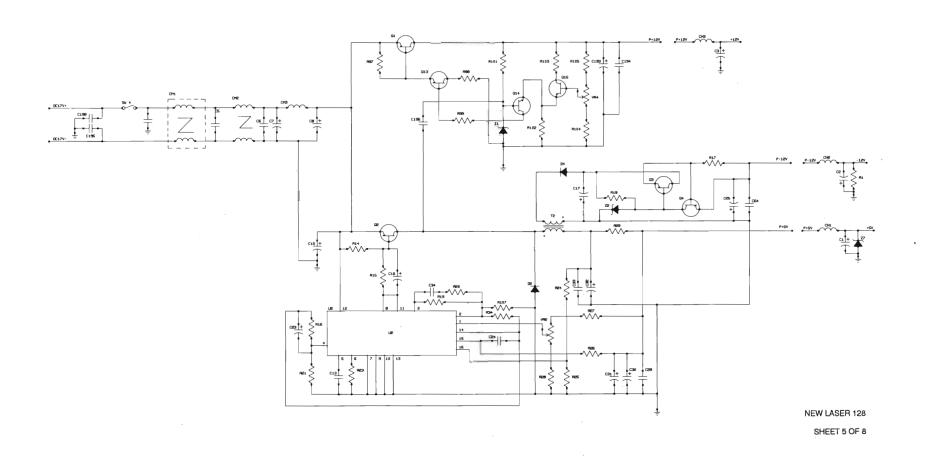

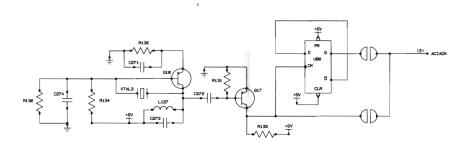

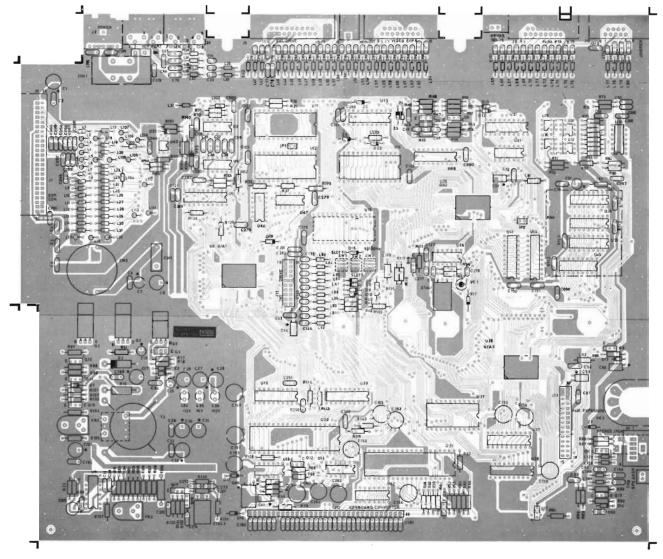

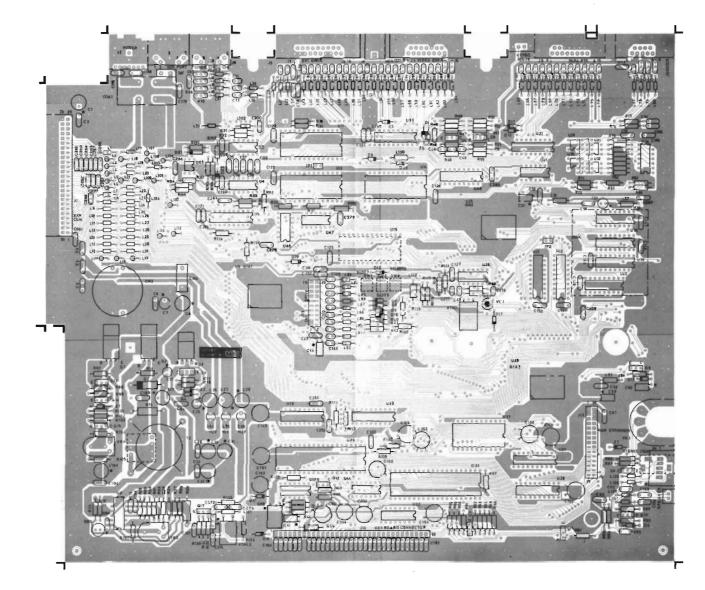

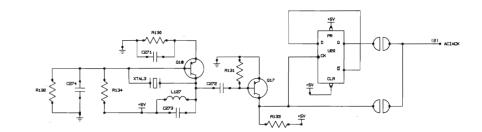

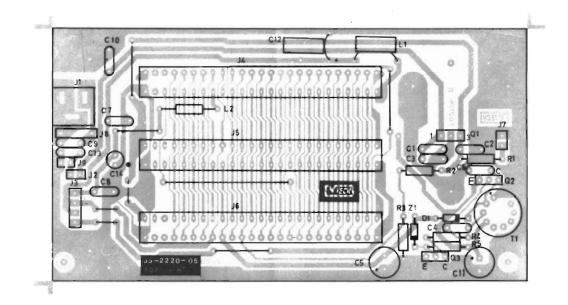

| D.4 | Schen  | natics, PCB and component |       |

|     | layout | 's                        | D-83  |

|     | D.4.1  | LASER 128                 | D-84  |

|     | D.4.2  | LASER 128EX               | D-87  |

|     | D.4.3  | LASER expansion box       | D-110 |

## CHAPTER 1 INTRODUCTION

#### 1. INTRODUCTION

This manual is primarily written for those users who need to know the software and hardware details of the computer in order to utilize its features more efficiently. These include application programmers, hardware designers as well as hobbyists. It provides specific information on the internal workings of the computer and is intended to be a technical supplement to the user's manual that comes with your computer.

#### 1.1 Organisation of manual

This manual can be conceptually divided into two sections.

Chapters 1 to 10 describe the functional and software aspects of the computer in a of view. programmer's point The and management of the organisation memory and I/O devices are described in detail. After going through these chapters, the reader should be able to access the resources on the computer directly, bypassing the built-in firmware. (Note: For compatibility reasons, access to these resources should be made through the builtin firmware whenever possible.)

Chapter 11 describes the hardware aspect of the computer. The entire circuit is divided into functional blocks and investigated one by one in depth.

This chapter is particularly useful for those service personnel who need to know the function of each component, the structure and organisation of the system buses, the general signal flow and timing waveforms of the various signals.

Besides, it also contains valuable information on the function and electrical characteristic of the signals on the various expansion connectors on the computer which is required by the peripheral hardware designers.

The appendices at the end of this manual provides supplementary information to the reader. These include schematics, PCB and component layouts, parts lists, gate-array pin assignments and data sheets for some of the major components used in the computer.

#### 1.2 Other sources of information

The materials provided in this manual is adhered to those technically inclined users. It assumes that the reader has some background knowledge on the basic structure and general operating principles of microcomputer systems and common peripheral devices.

The descriptions throughout this manual are clear, simple and easy to understand. Technical terms are avoided as far as possible and where they are used, they are explained clearly.

However if the reader happens to be a firsttime computer user, it is suggested that the reader should read some other reference books relevant subjects. on c.g. microprocessor system design, operating principles of peripheral devices such as disk drives and TV/monitors, assembly language programming etc., This will help the reader in understanding the materials described in this manual more thoroughly.

This manual focuses on the internals of the computer. To obtain further information on the installation and general operations of the computer, the readers are referred to the user's manual.

## CHAPTER 2 CENTRAL PROCESSING UNIT

#### 2. CENTRAL PROCESSING UNIT

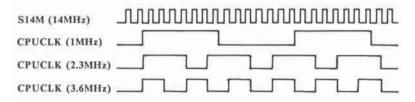

The computer uses 65C02, an enhanced version of its predecessor 6502, as its central processing unit. In the "LASER 128", 1 MHz version is used. In the "LASER 128 EX", 4 MHz version is used.

It has the following advantages compared with the NMOS 6502:

- Uses CMOS (Complementary Metal Oxide Semiconductor) technology to reduce power consumption and increase noise immunity.

- Completely static operation, no lowerlimit on CPU clock frequency (can be d.c.).

- Enhanced instruction set with new instructions and addressing modes.

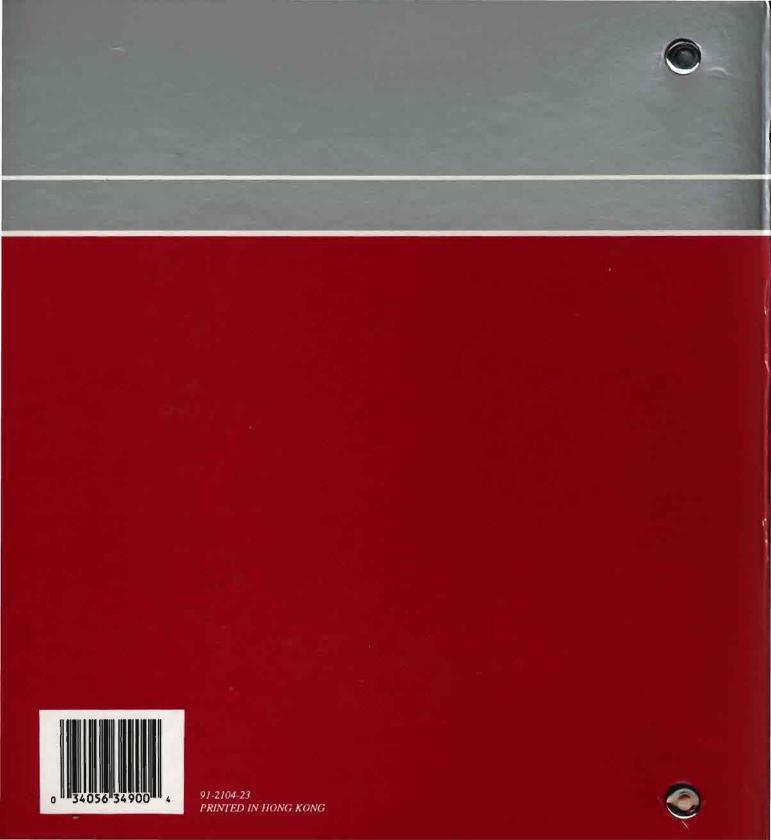

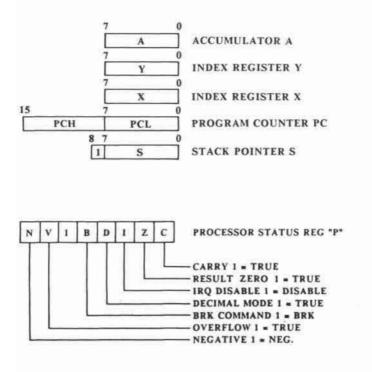

The 65C02 is a 8-bit microprocessor having 16 address lines to access a 64 K-byte address space. It has one 16-bit program counter, one 8-bit stack pointer, three 8-bit general purpose registers and one 8-bit processor status register. Figure 2-1 shows the programming model.

Fig. 2-1 Programming model of 65C02

The program counter "PC" is an 16-bit counter which keeps track of the address of the next instruction to be fetched and executed.

The stack pointer "S" is an 8-bit register which keeps track of the low-order eight bits of the address of the "top" of a 256-byte RAM stack maintained in \$0100 to \$01FF of the address space. The stack is primarily used for storing the subroutine call or interrupt return addresses. Use of the stack allows nested subroutine calls and multiple level interrupts. The accumulator "A" is an 8-bit general purpose register which is often used for storing the result of arithmetic and logical operations. It also forms one of the input operands for many of these operations.

The index registers "X" and "Y" are 8-bit registers which are usually used with the indexed addressing mode of the microprocessor. Use of these registers facilitates the manipulation of tables maintained in main memory.

The processor status register "P" is an 8-bit register which holds the internal state of the microprocessor and status of some arithmetic and logical operations.

The above is only a brief introduction to the 65C02 CPU. For more information, please refer to the data sheet and technical documentations published by the manufacturers.

2-4

### CHAPTER 3 MEMORY ORGANISATION

#### 3. MEMORY ORGANISATION

The ROM and RAM memory system will be investigated in this chapter.

#### 3.1 System address map

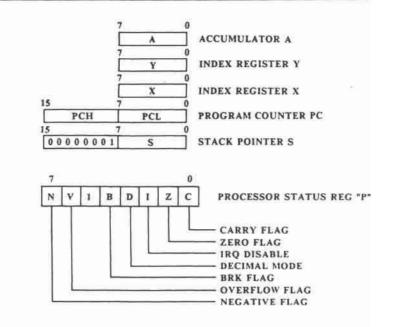

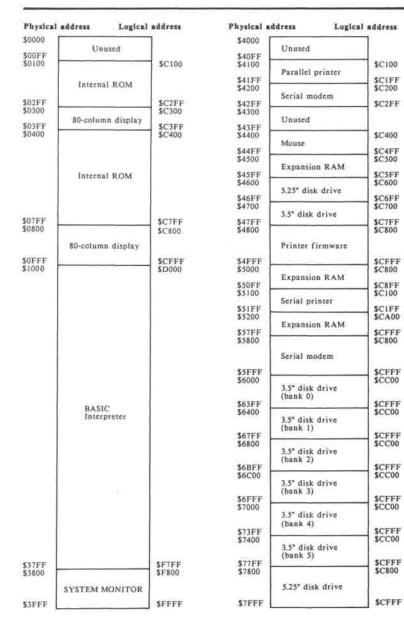

Figure 3-1 shows the system address map. The CPU address space can be divided into four areas:

- a) ROM (Read Only Memory)

- b) RAM (Random Access Memory)

- c) I/O (Input / Output)

- d) Hardware page

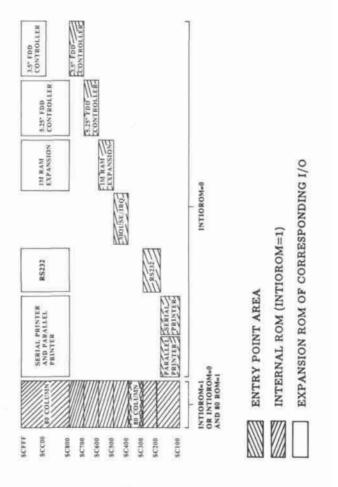

#### Fig. 3-1 System address map

The 65C02 has 16 address lines. It can only access 64K bytes of memory. In order to access more than 64K bytes of memory, the bank-switching technique is employed. There are bank registers to map the physical memory to the 64K-byte logical address space.

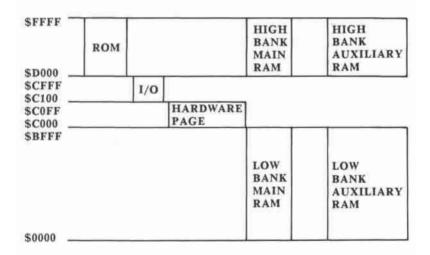

#### 3.2 ROM

The ROM consists of three parts:

- a) BASIC interpreter

- b) System monitor

- c) I/O drivers

Fig. 3-2 ROM mapping

INTIOROM is a soft-switch which controls the I/O ROM bank configuration. Softswitch is widely used in the computer. The logical state of the soft-switch is set by software. A summary of all soft-switches are listed in Table 3-5.

#### 3.2.1 The BASIC interpreter

The address range is from \$D000 to \$F7FF. Details of the BASIC commands can be found in the user's manual.

#### 3.2.2 The System Monitor

The monitor occupies \$F800 to \$FFFF. The basic I/O subroutines are in the monitor. You can enter the monitor from BASIC by typing CALL-151 and pressing RETURN.

#### 3.2.3 I/O firmwares

#### 3.2.3.1 I/O firmwares map

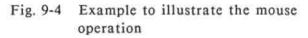

The mapping of the I/O firmwares are illustrated in Fig 3-3.

Fig. 3-3 I/O firmware areas

The only I/O firmware that remains active when INTIOROM is turned on is the 80column display driver. When INTIOROM remains inactive, i.e. INTIOROM = 0, the possible I/O activities are:

- parallel printer

- serial printer

- RS232

- 80-column text

- mouse

- 1 M RAM expansion

- FDD (Floppy Disk Drive) controller (5.25"/3.5")

At any one time, only one kind of printer can be used (either parallel or serial). This is selected by a switch on the front panel of the computer.

#### 3.2.3.2 I/O firmware control

a) INTIOROM = 1

If INTIOROM equals one, all the internal ROM area (\$C100 to \$CFFF) can be accessed freely.

b) INTIOROM = 0

If 80ROM is reset, then the internal \$C3XX (for 80-column) and its expansion ROM cannot be accessed. Should 80ROM be active, the 80-column firmware can be accessed. The 80-column expansion ROM can be accessed after reading from or writing to any location within \$C300 - \$C3FF. It is turned off by accessing \$CFFF.

For all I/O firmwares, their expansion ROM can be turned off by accessing \$CFFF.

If reading from or writing to that I/O firmware entry point region, their expansion ROM will be automatically turned on.

- The parallel printer and serial printer share the same expansion ROM (\$C800 -\$CFFF) so only one type of printer can be active at any one time.

- RS232 firmware occupies the memory address range \$C200 \$C2FF.

- The mouse firmware only occupies \$C400

\$C4FF. Accessing any location in this range cannot affect any \$C800-\$CFFF expansion ROM.

- The 1M RAM expansion firmware occupies locations from \$C500 \$C5FF.

- The 5.25" floppy disk drive controller firmware occupies locations from \$C600-\$C6FF.

- The 3.5" disk drive firmware occupies locations from \$C700 \$C7FF.

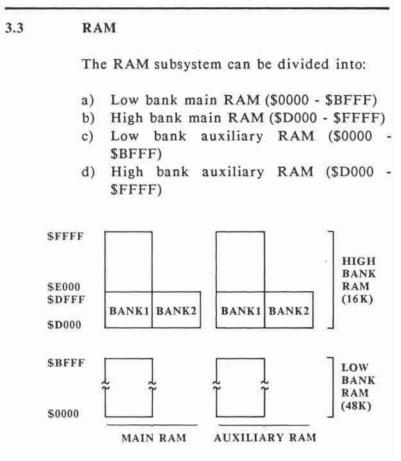

Fig. 3-4 RAM map

The operation of these memory banks will be discussed in detail in the following sections.

#### 3.3.1 RAM memory usage

Some RAM memory is dedicated for special functions due to the CPU and system requirement. However most of the RAM memory are free areas where the user's program can use. By knowing more of the RAM functional partition, the user can manage the RAM more efficiently.

Fig. 3-5 RAM memory usage map

#### · Page one

The 65C02 uses page 1 as its stack. When subroutine call or an interrupt occurs the microprocessor will push the return addresses onto the stack. Upon return from a subroutine or an interrupt the address will be pulled from stack. Many programs also use the stack for temporary storage of registers. The 65C02 operates the stack on a first-in, last-out basis.

· Page two

This is the keyboard input buffer used by the Monitor and the BASIC interpreter.

· Page three

The DOS and Monitor use it to store link addresses or vectors. Since only the upper part of page 3 is used by the computer, most of the page 3 area may be used freely.

| ADDRESS | FUNCTION                   |  |

|---------|----------------------------|--|

| 03F0    | BRK request vector used by |  |

| 03F1    | Monitor                    |  |

| 03F2    | Reset vector               |  |

| 03F3    | ŭ.                         |  |

| 03F4    | Power-up signature byte    |  |

| 03F5    | Jump instruction to the    |  |

| 03F6    | subroutine that handles    |  |

| 03F7    | BASIC "&" commands         |  |

| 03F8    | Jump instruction to the    |  |

| 03F9    | subroutine that handles    |  |

| 03FA    | user (CTRL - Y) commands   |  |

| 03FB    | Jump instruction to the    |  |

| 03FC    | routine that handles       |  |

| 03FD    | non-maskable interrupt.    |  |

| 03FE    | Interrupt Request vector   |  |

| 03FF    |                            |  |

#### Table 3-1 Page three vectors used by Monitor

#### · Video buffers

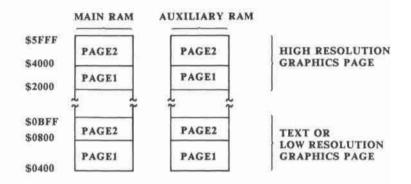

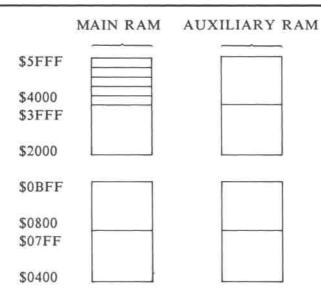

The text mode and low resolution graphics mode share the same display buffer. Page one is from \$0400 - \$07FF and page two is from \$0800 - \$0BFF. High resolution graphics page one uses \$2000 - \$3FFF and page two is from \$4000 - \$5FFF. If the display buffer is not used for display, it can be used by the user as program area.

• Free RAM area (\$6000 - \$BFFF)

The user's program can be freely placed in this RAM area.

#### 3.3.2 High-bank RAM memory (\$D000 - \$FFFF)

This RAM memory refers to address \$D000 - \$FFFF. An additional 4K RAM is placed next to \$D000 - \$DFFF as BANK 2.

This high-bank RAM can be freely selected as read-only, write-only, read/write or inhibited totally. It should be noted that this high-bank RAM occupies the same address range as ROM. Moreover, there are separate high-bank RAM areas for main and auxiliary RAM memory.

Fig. 3-6 High bank RAM memory mapping

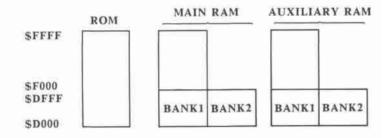

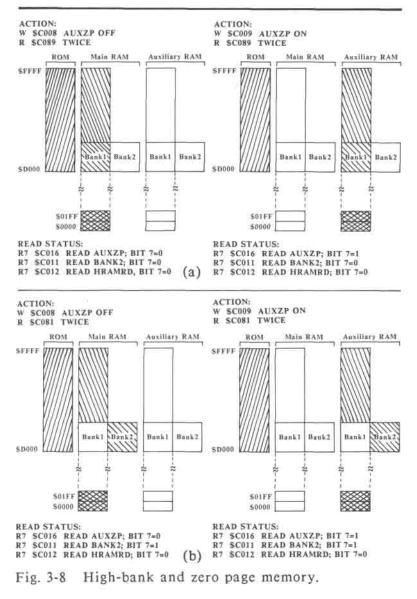

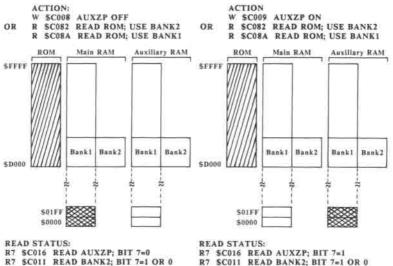

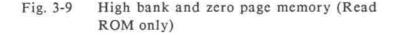

#### 3.3.2.1 High - Bank RAM Switches

To control the operation of the high-bank RAM, the switches in table 3-2 can be used. When power is turned on or CTRL-RESET is pressed, the high-bank RAM will always be set to write-enabled and ROM set to read enabled.

| Operation | Address                  | Function                                      |

|-----------|--------------------------|-----------------------------------------------|

| R         | \$C080<br>(or<br>\$C084) | Read high-<br>bank RAM<br>only; bank2         |

| R TWICE   | \$C081<br>(or<br>\$C085) | Read ROM,<br>write<br>high-bank<br>RAM; bank2 |

#### MEMORY ORGANISATION

| Operation | Address                  | Function                                                   |

|-----------|--------------------------|------------------------------------------------------------|

| R         | \$C082<br>or<br>\$C086)  | Read ROM<br>only                                           |

| R twice   | \$C083<br>(or<br>\$C087) | Read and<br>write high-<br>bank RAM;<br>bank2              |

| R         | \$C088<br>(or<br>\$C08C) | Read high-<br>bank RAM<br>only; bankl                      |

| R TWICE   | \$C089<br>(or<br>\$C08D) | Read ROM,<br>write high-<br>bank RAM;<br>bankl             |

| R         | \$C08A<br>(or<br>\$C08E) | Read ROM<br>only                                           |

| R TWICE   | \$C08B<br>(or<br>\$C08F) | Read and<br>write high-<br>bank RAM;<br>bank1              |

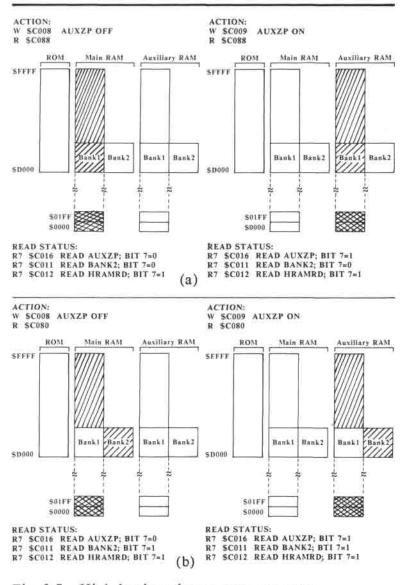

| W         | \$C008<br>(AUXZP)        | Off AUXZP;<br>use main<br>high-bank,<br>page 0 &<br>page 1 |

| Operation | Address                   | Function                                                          |

|-----------|---------------------------|-------------------------------------------------------------------|

| W         | \$C009<br>(AUXZP)         | On AUXZP;<br>use<br>auxiliary<br>high-bank,<br>page 0 &<br>page 1 |

| R7        | \$C016<br>(Read<br>AUXZP) | If bit 7=<br>1 then<br>auxiliary<br>bank RAM<br>is in use         |

|           |                           | If bit 7=0<br>then main<br>bank RAM<br>is in use.                 |

Table 3-2 RAM control hardware locations for Zero Page and high-bank (N.B. R=Read; W=write; R7=read bit 7 of the location)

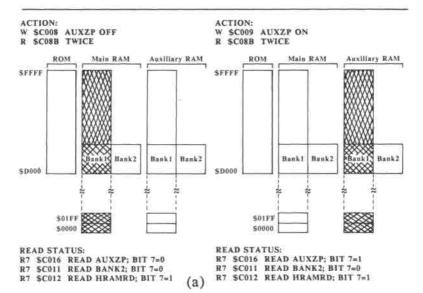

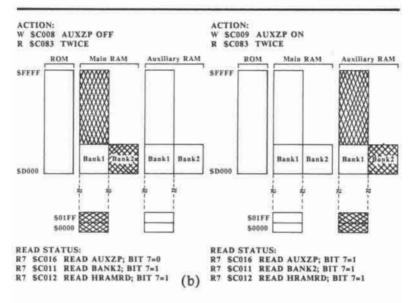

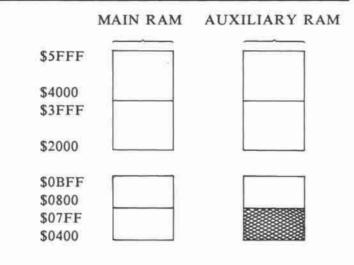

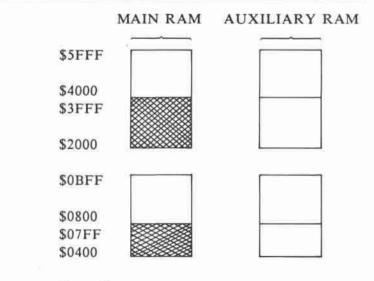

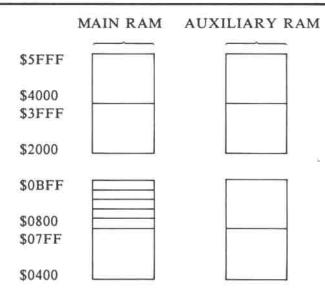

How the switches affect the high-bank memory are illustrated in Fig 3-7 to Fig 3-10.

#### MEMORY ORGANISATION

- (a) Read high-bank RAM bank 1 memory

- (b) Read high-bank RAM bank 2 memory

- Read ROM; write high-bank RAM bank 1 memory

- (b) Read ROM; write high-bank RAM bank 2 memory

#### MEMORY ORGANISATION

R7 \$C012 READ HRAMRD; BIT 7=0

R7 \$C012 READ HRAMRD; BIT 7=0

Fig. 3-10 High bank memory:

- (a) Read and write high-bank RAM bank1 memory

- (b) Read and write high-bank RAM bank2 memory

Read

#### 3.3.3 Low-bank RAM memory (\$0000 - \$BFFF)

The low-bank RAM can be divided into 2 parts according to bank control switches:

- Zero page (\$0000 \$00FF) RAM and the stack (\$0100 - \$01FF)

- RAM addresses from \$0200 \$BFFF

#### 3.3.3.1 Zero page RAM and the stack

This part of RAM can be controlled by the AUXZP switch as the high-bank RAM range. When AUXZP soft-switch is turned on, the auxiliary RAM page zero and stack (\$0000 - \$01FF) is read and write accessible. If AUXZP is off, the main RAM (\$0000 -\$01FF) is read and write accessible. The function of the soft-switches can be found in Fig. 3-7 to 3-10.

The user is advised to take care in using zero page because the 65C02 and system software use this area for storage of important parameters.

## 3.3.3.2 \$0200 - \$BFFF RAM memory

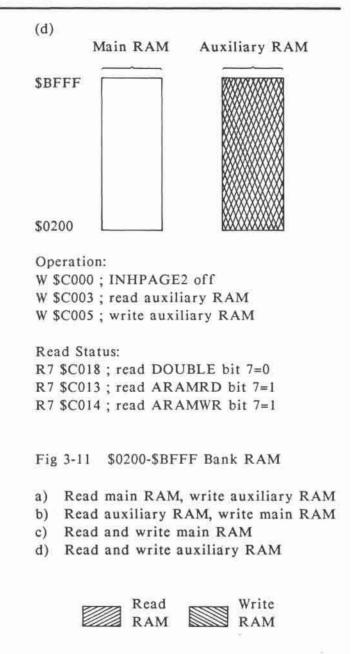

The switches which affect the read and write operation on this memory bank are shown in Table 3-3. However, the display buffer memory of either graphics or text mode is also within the range of \$0200 to \$BFFF. The display buffer memory switches have higher priority over memory control switches in Table 3-3, i.e. when the display buffer memory switches are effective, the ARAMRD and ARAMWR switches lose control over the display buffer memory. The display buffer memory will be discussed fully in the next section.

| Address | Operation | Function                                                |

|---------|-----------|---------------------------------------------------------|

| \$C002  | w         | off ARAMRD;<br>read main RAM<br>(\$0200-\$BFFF)         |

| \$C003  | w         | on ARAMRD;<br>read auxiliary<br>RAM (\$0200-<br>\$BFFF) |

| \$C004  | w         | off ARAMWR;<br>write main RAM<br>(\$0200-\$BFFF)        |

| Address | Operation | Function                                                     |

|---------|-----------|--------------------------------------------------------------|

| \$C005  | W         | on ARAMWR;<br>write auxiliary<br>RAM (\$0200 -<br>\$BFFF)    |

| \$C013  | R7        | read ARAMRD<br>status: If bit 7=1;<br>read auxiliary<br>RAM. |

|         |           | If bit 7=0; read<br>main RAM                                 |

| \$C014  | R7        | read ARAMWR<br>status: If bit 7=1<br>write auxiliary<br>RAM  |

|         |           | If bit 7=0; write<br>main RAM.                               |

## Table 3-3 \$0200-\$BFFF RAM bank switches

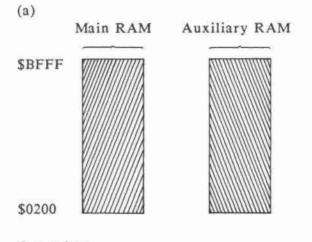

The ARAMRD and ARAMWR switches affect the READ / WRITE status of the \$0200-\$BFFF bank of RAM. These two switches operate independently. E.g. we can set main-RAM-read and auxiliary-RAMwrite.

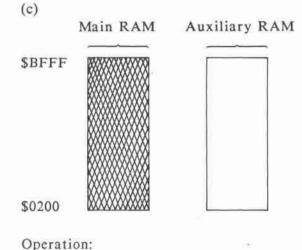

Operation:

- W \$C000; off INHPAGE2

- W \$C002; read main RAM

W \$C005; write auxiliary RAM

Read Status:

- R7 \$C018; read INHPAGE2 bit 7=0

- R7 \$C013 ; read ARAMRD bit 7=0

- R7 \$C014; read ARAMWR bit 7=1

W \$C000 ; INHPAGE2 off W \$C003 ; read auxiliary RAM W \$C004 ; write main RAM

Read Status: R7 \$C018 ; read INHPAGE2 bit 7=0 R7 \$C013 ; read ARAMRD bit 7=1 R7 \$C014 ; read ARAMWR bit 7=0

W \$C000 ; INHPAGE2 off W \$C002 ; read main RAM W \$C004 ; write main RAM

Read Status:

R7 \$C018 ; read INHPAGE2 bit 7=0 R7 \$C013 ; read ARAMRD bit 7=0 R7 \$C014 ; read ARAMWR bit 7=0

#### 3.3.3.3 Display buffer memory

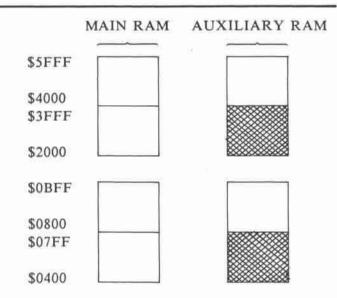

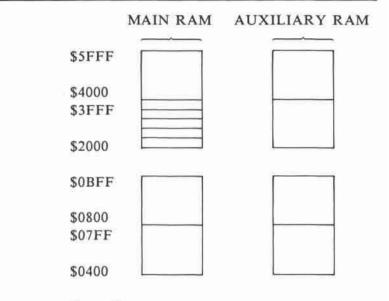

Fig. 3-12 illustrates the memory range covered by display buffer memory.

#### Fig. 3-12 Display buffer memory mapping

Since the display buffer memory overlaps with part of the low bank RAM, when the display buffer memory soft-switches are active, ARAMRD and ARAMWR will have no effect on these memory areas.

| Address | Operation | Function                                                                    |

|---------|-----------|-----------------------------------------------------------------------------|

| \$C000  | W         | off INHPAGE2;<br>ARAMRD and<br>ARAMWR control<br>the display<br>memory      |

| \$C001  | W         | on INHPAGE2;<br>DPAGE2 and<br>HGR control the<br>display memory             |

| \$C054  | R/W       | off DPAGE2;<br>refer to Fig. 3-13                                           |

| \$C055  | R/W       | on DPAGE2;<br>refer to Fig. 3-13                                            |

| \$C056  | R/W       | off HGR: turns<br>off high<br>resolution<br>graphics; refer to<br>Fig. 3-13 |

The switches affecting the display buffer memory are shown in Table 3-4.

| Address | Operation | Function                                                                                  |

|---------|-----------|-------------------------------------------------------------------------------------------|

| \$C057  | R/W       | on HGR; turns on<br>high resolution<br>graphics refer to<br>Fig. 3-13                     |

| \$C018  | R7        | Read INHPAGE2<br>status:<br>If bit 7 = 1;<br>INHPAGE2 on<br>If bit 7 = 0;<br>INHPAGE2 off |

| \$C01C  | R7        | Read DPAGE2<br>status:<br>If bit 7 = 1;<br>DPAGE2 on<br>If bit 7 = 0;<br>DPAGE2 off       |

| \$C01D  | R7        | Read HGR status:<br>If bit 7 = 1;<br>HGR on<br>If bit 7 = 0;<br>HGR off                   |

Table 3-4 Display buffer memory switches

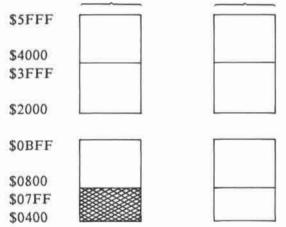

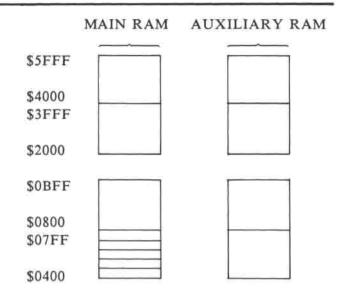

In Fig. 3-13 the operational relation between INHPAGE2, DPAGE2 and HGR is shown. It should be noted that when INHPAGE2 is off, ARAMRD and ARAMWR control the reading or writing of the RAM. The DPAGE2 switch only affects the display. The relation between DPAGE2 and display memory is shown in Fig. 3-14.

# MAIN RAM AUXILIARY RAM

Operation:

W \$C001; on INHPAGE 2 W \$C054; off DPAGE2 W \$C056; off HGR

#### Read status:

R7 \$C018; Read INHPAGE2; bit 7=1 R7 \$C01C; Read DPAGE2; bit 7=0 R7 \$C01D; Read HGR; bit 7=0

INHPAGE2 on HGR off and DPAGE2 off

Operation: W \$C001; on INHPAGE2 W \$C055; on DPAGE2 W \$C056; off HGR

Read status: R7 \$C018; Read INHPAGE2; bit 7=1 R7 \$C01C; Read DPAGE2; bit 7=1 R7 \$C01D; Read HGR; bit 7=0

(b) INHPAGE2 on, HGR off and DPAGE2 on

Operation: W \$C001; on INHPAGE2 W \$C054; off DPAGE2 W \$C057; on HGR

Read status: R7 \$C018; Read INHPAGE2; bit 7=1 R7 \$C01C; Read DPAGE2; bit 7=0 R7 \$C01D; Read HGR; bit 7=1

(c) INHPAGE2 on, HGR on and DPAGE2 off.

Operation: W \$C001; on INHPAGE2 W \$C055; on DPAGE2 W \$C057; on HGR

```

Read status:

R7 $C018; Read INHPAGE2; bit 7=1

R7 $C01C; Read DPAGE2; bit 7=1

R7 $C01D; Read HGR; bit 7=1

```

RAM read and write

(d) INHPAGE2 on, HGR on and DPAGE2 on.

Fig. 3-13 Display buffer switching

\* When INHPAGE2 is off, ARAMRD and ARAMWR will control which bank of RAM to be read or written.

Operation: R/W \$C054; off DPAGE2 R/W \$C056; off HGR

(a) INHPAGE2 off, HGR off and DPAGE2 off.

Operation: R/W \$C055; on DPAGE2 R/W \$C056; off HGR

(b) INHPAGE2 off, HGR off and DPAGE2 on.

Operation: R/W \$C054; off DPAGE2 R/W \$C057; on HGR R/W \$C050; off TEXT

(c) INHPAGE2 off, HGR on and DPAGE2 off.

```

Operation:

R/W $C055; on DPAGE2

R/W $C057; on HGR

R/W $C050; off TEXT

```

memory to be displayed on screen

Fig. 3-14 Selection of video display buffer

When in double resolution modes, display buffer (\$0400-\$07FF or \$2000-\$3FFF) of auxiliary RAM will display simultaneously with display buffer (\$0400-\$07FF or \$2000-\$3FFF) of main RAM. The setting of DPAGE2 will lose control in these modes.

### 3.4 Hardware page (\$C000 - C0FF)

There is no physical RAM or ROM in this page. This page is important to the operation of the system because all the softswitches and their status bits are in this page. The operation of these soft-switches can be found in details in various chapters of this manual.

| Location | Operation | Description                                      |

|----------|-----------|--------------------------------------------------|

| C00X     | R         | BIT 7=KEY<br>STROBE; BIT 0-6<br>KEYBOARD<br>DATA |

| C000     | w         | OFF INHPAGE2                                     |

| C001     | w         | ON INHPAGE2                                      |

| C002     | w         | OFF ARAMRD                                       |

| C003     | w         | ON ARAMRD                                        |

| C004     | w         | OFF ARAMWR                                       |

| C005     | w         | ON ARAMWR                                        |

| C006     | w         | OFF INTIOROM                                     |

| C007     | w         | ON INTIOROM                                      |

| C008     | w         | OFF AUXZP                                        |

| Location | Operation | Description                           |

|----------|-----------|---------------------------------------|

| C009     | w         | ON AUXZP                              |

| C00A     | w         | OFF 80ROM                             |

| C00B     | w         | ON 80ROM                              |

| C00C     | w         | OFF DBLRES                            |

| C00D     | w         | ON DBLRES                             |

| C00E     | w         | OFF CHARSET2                          |

| C00F     | W         | ON CHARSET2                           |

| C01X     | w         | RESET KEY<br>STROBE                   |

| C010     | R         | BIT 7=1; A KEY<br>IS BEING<br>PRESSED |

| C011     | R         | BIT 7=1; BANK2<br>ON                  |

| C012     | R         | BIT 7=1;<br>HRAMRD ON                 |

| C013     | R         | BIT 7=1;<br>ARAMRD ON                 |

| C014     | R         | BIT 7=1;<br>ARAMWR ON                 |

| Location | Operation | Description                                    |

|----------|-----------|------------------------------------------------|

| C015     | R         | BIT 7=1;<br>INTIOROM ON                        |

| C016     | R         | BIT 7=1; AUXZP<br>ON                           |

| C017     | R         | BIT 7=1; 80ROM<br>ON                           |

| C018     | R         | BIT 7=1;<br>INHPAGE2 ON                        |

| C019     | R         | BIT 7=1;<br>VERTICAL<br>BLANKING<br>NOT ACTIVE |

| C01A     | R         | BIT 7=1; TEXT<br>ON                            |

| C01B     | R         | BIT 7=1; MIX<br>ON                             |

| C01C     | R         | BIT 7=1;<br>DPAGE2 ON                          |

| C01D     | R         | BIT 7=1; HGR<br>ON                             |

| C01E     | R         | BIT 7=1;<br>CHARSET2 ON                        |

| Location | Operation | Description |

|----------|-----------|-------------|

| C01F     | R         | BIT 7=1;    |

|          |           | DBLRES ON   |

| C02X     | R/W       | RESERVED    |

| C03X     | R/W       | TOGGLE      |

|          |           | SPEAKER     |

|          |           | OUTPUT      |

| C04X     | R/W       | RESERVED    |

| 2050     | R/W       | OFF TEXT    |

| C051     | R/W       | ON TEXT     |

| C052     | R/W       | OFF MIX     |

| C053     | R/W       | ON MIX      |

| C054     | R/W       | OFF DPAGE2  |

| C055     | R/W       | ON DPAGE2   |

| C056     | R/W       | OFF HGR     |

| C057     | R/W       | ON HGR      |

| C058-    | R/W       | RESERVED    |

| C05D     |           |             |

| C05E     | R/W       | OFF         |

|          |           | INHDRGR     |

| Location      | Operation | Description                                |

|---------------|-----------|--------------------------------------------|

| C05F          | R/W       | ON INHDRGR                                 |

| C06X          | w         | RESERVED                                   |

| C060          | R         | BIT 7=1; 40/80<br>SWITCH TO 40<br>POSITION |

| C061          | R         | READ SWITCH<br>INPUT 0 OR 🖾                |

| C062          | R         | READ SWITCH<br>INPUT 1 OR 🔺                |

| C063          | R         | READ MOUSE<br>BUTTON                       |

| C064          | R         | READ TIMER 0                               |

| C065          | R         | READ TIMER 1                               |

| C066          | R         | READ MOUSE<br>XDIR                         |

| C067          | R         | READ MOUSE<br>YDIR                         |

| C068-<br>C06F | R         | RESERVED                                   |

| Location | Operation | Description  |

|----------|-----------|--------------|

| C07X     | R/W       | RESET        |

|          |           | VERTICAL     |

|          |           | BLANKING     |

|          |           | INTERRUPT    |

|          |           | AND JOYSTICK |

|          |           | PORT TIMERS  |

| C080-    | w         | RESERVED     |

| C08F     |           |              |

| C080     | R         | READ HIGH    |

|          |           | BANK 2 RAM   |

| C081     | R TWICE   | READ ROM     |

|          |           | AND WRITE    |

|          |           | HIGH BANK 2  |

|          |           | RAM          |

| C082     | R         | READ ROM     |

| C083     | R TWICE   | READ AND     |

|          |           | WRITE HIGH   |

|          |           | BANK 2 RAM   |

| C084-    | R         | REPEAT C080- |

| C087     |           | C083         |

|          |           | FUNCTION     |

| C088     | R         | READ HIGH    |

|          |           | BANK 1 RAM   |

| Location | Operation | Description  |

|----------|-----------|--------------|

| C089     | R TWICE   | READ ROM     |

|          | 5         | AND WRITE    |

|          |           | HIGH BANK 1  |

|          |           | RAM          |

| C08A     | R         | READ ROM     |

| C08B     | R TWICE   | READ AND     |

|          |           | WRITE HIGH   |

|          |           | BANK 1 RAM   |

| C08C-    | R         | REPEAT C088- |

| C08F     |           | C08B         |

|          |           | FUNCTION     |

| C090-    | R/W       | RESERVED     |

| C097     |           |              |

| C098     | R/W       | ACIA1        |

|          | ·.        | RECEIVE/     |

|          |           | TRANSMIT     |

|          |           | DATA         |

|          |           | REGISTER     |

| C099     | R/W       | ACIA1 STATUS |

|          |           | REGISTER     |

| C09A     | R/W       | ACIA1        |

|          | 3.        | COMMAND      |

|          |           | REGISTER     |

| Location      | Operation | Description  |

|---------------|-----------|--------------|

| C09B          | R/W       | ACIAI        |

|               | 0         | CONTROL      |

|               |           | REGISTER     |

| C09C-<br>C09F | R/W       | RESERVED     |

| C0A0-<br>C0A7 | R/W       | RESERVED     |

| C0A8          | R/W       | ACIA2        |

|               |           | RECEIVE/     |

|               |           | TRANSMIT     |

|               |           | DATA         |

|               |           | REGISTER     |

| C0A9          | R/W       | ACIA2 STATUS |

|               |           | REGISTER     |

| COAA          | R/W       | ACIA2        |

|               |           | COMMAND      |

|               |           | REGISTER     |

| COAB          | R/W       | ACIA2        |

|               |           | CONTROL      |

|               |           | REGISTER     |

| COAC-         | R/W       | RESERVED     |

| COAF          |           |              |

| COBX          | R/W       | RESERVED     |

| Location      | Operation | Description                                      |

|---------------|-----------|--------------------------------------------------|

| C0C0-<br>C0C7 | R         | RESERVED                                         |

| C0C0          | w         | ON MOUSE X-<br>DIR RISING-<br>EDGE<br>INTERRUPT  |

| C0C1          | w         | ON MOUSE X-<br>DIR FALLING-<br>EDGE<br>INTERRUPT |

| C0C2          | W         | ON MOUSE Y-<br>DIR RISING-<br>EDGE<br>INTERRUPT  |

| C0C3          | w         | ON MOUSE Y-<br>DIR FALLING-<br>EDGE<br>INTERRUPT |

| C0C4          | w         | OFF MOUSE<br>INTERRUPT<br>SOURCE                 |

| COC5          | w         | ON MOUSE<br>INTERRUPT<br>SOURCE                  |

| Location      | Operation | Description              |

|---------------|-----------|--------------------------|

| C0C6          | w         | OFF VERTICAL<br>BLANKING |

|               |           | INTERRUPT                |

| C0C7          | w         | ON VERTICAL              |

|               |           | BLANKING                 |

|               |           | INTERRUPT                |

| C0C8-<br>C0CE | w         | RESERVED                 |

| C0C8          | R         | BIT 7=1/0;               |

|               |           | MOUSE X-DIR              |

|               |           | FALLING/                 |

|               |           | RISING EDGE              |

|               |           | INTERRUPT                |

|               |           | SELECTED                 |

| C0C9          | R         | BIT 7=1/0;               |

|               |           | MOUSE Y-DIR              |

|               |           | FALLING/                 |

|               |           | RISING EDGE              |

|               |           | INTERRUPT                |

|               |           | SELECTED                 |

| COCA          | R         | BIT 7=1; MOUSE           |

|               |           | INTERRUPT                |

|               |           | ENABLED                  |

| Location | Operation | Description    |

|----------|-----------|----------------|

| COCB     | R         | BIT 7=1;       |

|          |           | VERTICAL       |

|          |           | BLANKING       |

|          |           | INTERRUPT      |

|          |           | ENABLED        |

| C0CC     | R         | BIT 7=1; MOUSE |

|          |           | X-DIR          |

|          |           | INTERRUPT      |

|          |           | OCCURRED       |

| COCD     | R         | BIT 7=1; MOUSE |

|          |           | Y-DIR          |

|          |           | INTERRUPT      |

|          |           | OCCURRED       |

| C0CF     | R         | RESERVED       |

| C0CF     | w         | RESET MOUSE    |

|          | 4         | INTERRUPT      |

| C0D0-    | R/W       | RESERVED FOR   |

| C0D3     | N         | EXPANSION      |

|          |           | RAM            |

|          |           | CONTROL        |

| C0D4-    | R/W       | RESERVED       |

| C0DF     |           |                |

| Location | Operation | Description  |

|----------|-----------|--------------|

| COEX     | R/W       | RESERVED FOR |

|          |           | FLOPPY DISK  |

|          |           | DRIVE        |

|          |           | CONTROL      |

| C0FX     | R/W       | RESERVED     |

- NOTE 1: Read \$C010 to \$C01F will read the keyboard code (bit 0-bit 6) and reading \$C010 resets KEYSTROBE too.

- NOTE 2: \$C081, \$C083, \$C089 and \$C08B have to be read twice to achieve the described function in the table.

- Table 3-5 Hardware page locations.

## CHAPTER 4 KEYBOARD AND SPEAKER

#### 4. KEYBOARD AND SPEAKER

Among the various I/O devices for the computer, the keyboard, speaker and video display are most commonly used. In this chapter, we will focus on the keyboard and the speaker, while the video display will be discussed in the next chapter.

#### 4.1 Keyboard

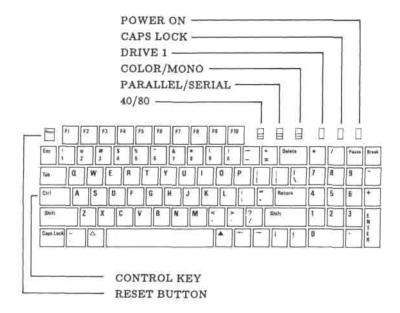

The keyboard of the computer has a typewriter layout, a numeric keypad and ten function keys. The specifications of the keyboard are listed in Table 4-1.

| 8  | 90                  |

|----|---------------------|

| 1  | ASCII               |

|    |                     |

|    | 10 function keys, 🔺 |

|    | and 🛆               |

|    | CONTROL - RESET     |

| ÷) |                     |

| 5  | Auto-repeat         |

|    | 8                   |

Table 4-1 Keyboard specifications

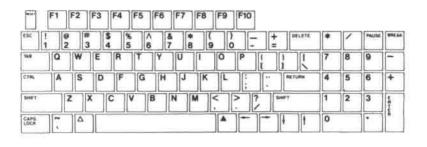

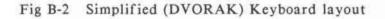

The computer keyboard layout can be changed by the keyboard switch on the back panel. Keyboard layout is selectable between standard U.S.A. and alternate Dvorak layout using the STD/ALT KBD switch on the back panel of the computer.

(NOTE: some versions do not have the keyboard switch and only standard U.S.A. layout is available).

Fig. 4-1 Keyboard switches and indicator lights.

| Fesser  | FI    | F   | 2 | F3     | FA | F5     | F6 | \$7 | FI | FS | F1 | a  |   |        | Ľ | ] [ |       |       |

|---------|-------|-----|---|--------|----|--------|----|-----|----|----|----|----|---|--------|---|-----|-------|-------|

| Esc     | ;     | 2   |   | #<br>3 | 5  | %<br>5 | 5  | 8   | *  | 1  | 1  | -  | • | Dates  | • | 1   | Pause | Brouk |

| Tab     | 1     | 0   | W | E      | ٦  | R      | T  | YU  | 1  |    | 0  | P  |   |        | 7 | 8   | 9     | -     |

| Cul     | ٦     | A   | S | ī      | D  | F      | G  | H   | J  | ĸ  | L  |    |   | Return | 4 | 5   | 6     | +     |

| Shift   | _     | Z   | ٦ | x      | C  | V      | В  | N   | M  | V. | 2  | 17 | 1 | ihite  | 1 | 2   | 3     | EN    |

| Caps Le | ick - | - 1 |   | T      |    |        |    |     |    | 7  | -  | -1 | - | 1 1    | 0 | 1-  | í     | TE    |

Fig. 4-2 (a) Keyboard switch set to STD (The USA standard keyboard)

| Remo    | Ft.   | F      | 2  | F3 | FA | F5 | Ħ |    | F7 | FB | F9 | F      | 10 | E  |       |       | E | ] [ |       |       |

|---------|-------|--------|----|----|----|----|---|----|----|----|----|--------|----|----|-------|-------|---|-----|-------|-------|

| Esc     | 1     | 0<br>2 | ]; |    | \$ | 5  | 6 | 1  |    | *  | 1. | 1<br>U | Ī  |    | D     | elete | • | 1   | Pause | Benak |

| Tah     | זר    |        | <  | >  | P  |    | Y | F  | 6  |    |    | я      | L  | ][ | 1:    | K     | 7 | 8   | 9     | *     |

| Ctrl    | Ï     | A      | 0  | E  |    | IJ | 1 | 0  | 1  | i  | T  | N      | S  | 1- | Ret   | urn   | 4 | 5   | 6     | +     |

| Shift   | _     | 1      | T  | 0  | J  | K  | X | T  | B  | M  | W  | V      |    | z  | Shift |       | 1 | 2   | 3     | EN    |

| Caps Lo | ick - | 4      |    | ī  | -  |    |   | _/ |    |    | 7  | •      | -  | 1- | 10    | 1     | 0 |     | iFi   | E     |

Fig. 4-2 (b) Keyboard switch is set to ALT (The simplified keyboard)

There are 3 indicator lights on the front panel. They are

- POWER when power is turned on, the light will be on

- b) DISK when the built-in drive is accessed, this light will glow.

- c) CAPSLOCK when this light glows, it indicates that the keyboard is in capslock mode, that is all letter keys will produce capital letters on the screen irrespective of the position of the shift keys.

The keyboard will generate ASCII code when any one key of the keyboard is pressed. The keys to generate ASCII codes are tabulated in Table 4-2.

Table 4-2 Keys & the ASCII codes

| KEY       | NORMAL | CHAR  | CTRL | CHAR | SHIFT | CHAR | вотн | CHAR |

|-----------|--------|-------|------|------|-------|------|------|------|

| DELETE    | 7F     | DEL   | 7F   | DEL  | 7F    | DEL  | 7F   | DEL  |

| -         | 08     | BS    | 08   | BS   | 08    | BS   | 08   | BS   |

| TAB       | 09     | HT    | 09   | нт   | 09    | HT   | 09   | HT   |

|           | 0 A    | LF    | 0A   | LF   | 0A    | LF   | 0A   | LF   |

| TTT I     | 0B     | VT    | 0B   | VT   | OB    | VT   | 0B   | VT   |

| RETURN    | 0D     | CR    | 0D   | CR   | 0D    | CR   | 0D   | CR   |

| -         | 15     | NAK   | 15   | NAK  | 15    | NAK  | 15   | NAK  |

| [ESC]     | 1B     | ESC   | 1B   | ESC  | 1B    | ESC  | 1B   | ESC  |

| [SPACE]   | 20     | SP    | 20   | SP   | 20    | SP   | 20   | SP   |

|           | 27     |       | 27   | ×    | 22    |      | 22   | 1.00 |

| , <       | 2C     | â.    | 2C   | 6    | 3C    | <    | 3C   | <    |

| (*)       | 2D     |       | 1F   | US   | 5F    | -    | 1F   | US   |

| . >       | 2E     | - A 2 | 2E   | ×    | 3E    | >    | 3E   | >    |

| / ?       | 2F     | 1     | 2F   | 1    | 3F    | ?    | 3F   | ?    |

| 0)        | 30     | 0     | 30   | 0    | 29    | )    | 29   | )    |

| 1 1       | 31     | 1     | 31   | 1    | 21    | 1    | 21   | 1    |

| 2 @       | 32     | 2     | 00   | NUL  | 40    | @    | 00   | NUL  |

| 3 #       | 33     | 3     | 33   | 3    | 23    | #    | 23   | #    |

| 4 \$      | 34     | 4     | 34   | 4    | 24    | \$   | 24   | \$   |

| 5 %       | 35     | 5     | 35   | 5    | 25    | 9%   | 25   | %    |

| 6 ^       | 36     | 6     | 1E   | RS   | 5E    | ~    | 1E   | RS   |

| 7 &       | 37     | 7     | 37   | 7    | 26    | 80   | 26   | &    |

| 8 .       | 38     | 8     | 38   | 8    | 2A    |      | 2A   |      |

| 9 (       | 39     | 9     | 39   | 9    | 28    | (    | 28   | (    |

| : :       | 3B     | 3     | 3B   | 1    | 3A    | :    | 3A   | :    |

| = +       | 3D     | -     | 3D   | -    | 2B    | +    | 2B   | +    |

| 1 (       | 5B     | 1     | 1B   | ESC  | 7B    | (    | 1B   | ESC  |

| NT =      | 5C     | 1     | 1C   | FS   | 7C    | 3    | 1C   | FS   |

| 1.1       | 5D     | 1     | 1D   | GS   | 7D    | )    | 1D   | GS   |

| · · · · · | 60     |       | 60   | 4    | 7E    | ~    | 7E   | ~    |

| A         | 61     | a     | 01   | SOH  | 41    | A    | 01   | SOH  |

| в         | 62     | b     | 02   | STX  | 42    | в    | 02   | STX  |

| C         | 63     | c     | 03   | ETX  | 43    | С    | 03   | ETX  |

| D         | 64     | d     | 04   | EOT  | 44    | D    | 04   | EOT  |

| E         | 65     | e     | 05   | ENQ  | 45    | E    | 05   | ENQ  |

| F         | 66     | f     | 06   | ACK  | 46    | F    | 06   | ACK  |

| G         | 67     | g     | 07   | BEL  | 47    | G    | 07   | BEL  |

| н         | 68     | h     | 08   | BS   | 48    | н    | 08   | BS   |

| I         | 69     | 1     | 09   | HT   | 49    | I    | 09   | HT   |

| 3         | 6A     | j     | 0A   | LF   | 4A    | J    | 0.4  | LF   |

| к         | 6B     | k     | 0B   | VT   | 4B    | K    | 0B   | VT   |

#### KEYBOARD AND SPEAKER

| KEY   | NORMAL | CHAR | CTRL | CHAR | SHIFT | CHAR | вотн | CHAR         |

|-------|--------|------|------|------|-------|------|------|--------------|

| L     | 6C     | ĩ    | 0C   | FF   | 4C    | L    | 0C   | FF           |

| M     | 6D     | m    | 0D   | CR   | 4D    | M    | 0D   | CR           |

| N     | 6E     | п    | 0E   | SO   | 4E    | N    | 0E   | SO           |

| 0     | 6F     | 0    | 0F   | SI   | 4F    | 0    | OF   | SI           |

| P     | 70     | р    | 10   | DLE  | 50    | P    | 10   | DLE          |

| Q     | 71     | q    | 11   | DC1  | 51    | Q    | 11   | DC1          |

| R     | 72     | r    | 12   | DC2  | 52    | R    | 12   | DC2          |

| S     | 73     | s    | 13   | DC3  | 53    | S    | 13   | DC3          |

| т     | 74     | 1    | 14   | DC4  | 54    | т    | 14   | DC4          |

| U     | 75     | u    | 15   | NAK  | 55    | U    | 15   | NAK          |

| v     | 76     | v    | 16   | SYN  | 56    | V    | 16   | SYN          |

| W     | 77     | w    | 17   | ETB  | 57    | W    | 17   | ETB          |

| X     | 78     | x    | 18   | CAN  | 58    | x    | 18   | CAN          |

| Y     | 79     | У    | 19   | EM   | 59    | Y    | 19   | EM           |

| Z     | 7A     | z    | 1A   | SUB  | 5A    | Z    | 1A   | SUB          |

| 0     | 30     | 0    | 30   | 0    | 30    | 0    | 30   | 0            |

| 1     | 31     | 1    | 31   | 1    | 31    | 1    | 31   | 1            |

| 2     | 32     | 2    | 32   | 2    | 32    | 2    | 32   | 2            |

| 3     | 33     | 3    | 33   | 3    | 33    | 3    | 33   | 3            |

| 4     | 34     | 4    | 34   | 4    | 34    | 4    | 34   | 4            |

| 5     | 35     | 5    | 35   | 5    | 35    | 5    | 35   | 5            |

| 6     | 36     | 6    | 36   | 6    | 36    | 6    | 36   | 6            |

| 7     | 37     | 7    | 37   | 7    | 37    | 7    | 37   | 7            |

| 8     | 38     | 8    | 38   | 8    | 38    | 8    | 38   | 8            |

| 9     | 39     | 9    | 39   | 9    | 39    | 9    | 39   | 9            |

| ÷.    | 2E     | ÷.   | 2E   |      | 2E    | 5. C | 2E   | ÷.           |

|       | 2B     | +    | 2B   | +    | 2B    | +    | 2B   | +            |

|       | 2D     |      | 2D   | 1.00 | 2D    | 3.00 | 2D   |              |

| •     | 2A     |      | 2A   | •    | 2A    | 3•0  | 2A   | 2 <b>9</b> 0 |

| 1     | 2F     | 1    | 2F   | 1    | 2F    | 1    | 2F   | 1            |

| PAUSE | 13     | DC3  | 13   | DC3  | 13    | DC3  | 13   | DC3          |

| BREAK | 03     | ETX  | 03   | ETX  | 03    | ETX  | 03   | ETX          |

| ENTER | 0D     | CR   | 0D   | CR   | 0D    | CR   | 0D   | CR           |

| FI    | 00     | NUL  | 0    | NUL  | 0     | NUL  | 0    | NUL          |

| F2    | 01     | SOH  | 1    | SOH  | 1     | SOH  | 1    | SOH          |

| F3    | 02     | STX  | 2    | STX  | 2     | STX  | 2    | STX          |

| F4    | 03     | ETX  | 3    | ETX  | 3     | ETX  | 3    | ETX          |

| F5    | 04     | EOT  | 4    | EOT  | 4     | EOT  | 4    | EOT          |

| F6    | 05     | ENQ  | 5    | ENQ  | 5     | ENQ  | 5    | ENQ          |

| F7    | 06     | ACK  | 6    | ACK  | 6     | ACK  | 6    | ACK          |

| F8    | 07     | BEL  | 7    | BEL  | 7     | BEL  | 7    | BEL          |

| F9    | 0C     | FF   | 0C   | FF   | 0C    | FF   | 0C   | FF           |

| [F10] | 18     | CAN  | 18   | CAN  | 18    | CAN  | 18   | CAN          |

4-5

## 4.1.1 Accessing the keyboard

The keyboard input status and the ASCII keycode can be accessed by reading the hardware locations in Table 4-3.

| Address | Operation | Function        |

|---------|-----------|-----------------|

| \$C00X  | R7        | Bit 7=1; a      |

|         |           | key has         |

|         |           | been pressed    |

|         |           | Bit 7=0; no key |

|         |           | has ever been   |

|         |           | pressed         |

|         |           | Bit 0-6         |

|         |           | ASCII codc      |

|         |           | of the pressed  |

|         |           | key             |

| \$C010  | R7        | Bit 7=1; Any    |

| 2.5     |           | key is being    |

|         |           | pressed down    |

|         |           | Bit 7=0; No     |

|         |           | key is          |

|         |           | being           |

|         |           | pressed         |

|         |           | down            |

|         |           |                 |

| \$C01X  | R         | Bit 0-6; ASCII  |

|         |           | code of the     |

|         |           | pressing key    |

| Address | Operation | Function                               |

|---------|-----------|----------------------------------------|

| \$C010  | R/W       | reset the<br>keyboard strobe<br>latch  |

| \$C01X  | W         | reset the<br>kcyboard strobe<br>latch. |

Table 4-3 keyboard hardware locations

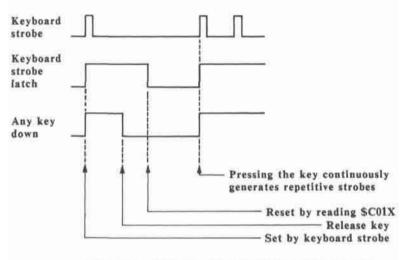

When any key is pressed, the keyboard strobe latch is set to 1. This keyboard strobe status can be read at bit 7 of location \$C00X. At the same time, the ASCII code of that key is also contained in bit 0-6. Reading \$C01X can also read the ASCII code, but it will reset the keyboard strobe status. To check if any key is being pressed down, the location \$C010 can be read but it will reset the keyboard strobe status at the same time. Usually we can check \$C00X first to see if any key has been pressed before, then we can read the ASCII code by reading \$C01X. Fig. 4-3 illustrates this event.

Fig. 4-3 Timing of pressing a key on the keyboard

The keyboard encoding IC has an autorepeat function. If a key is constantly held down, then that key will be generated automatically at a fixed rate.

## 4.1.2 Special function keys and switches

There are some keys which do not generate any ASCII code. These keys affects the system immediately.

Pressing these two keys simultaneously will reset the microcomputer system.

The status of these two keys can be read from locations \$C061 and \$C062 respectively. These two keys can be used as game control keys.

This is a toggling switch. When upper-case letters are activated, the CAPS LOCK indication light will glow.

d) 40 / 80 switch

80 column text mode can be turned on only when the 40 / 80 switch is set to 80 position.

| Address | Operation | Function                                       |

|---------|-----------|------------------------------------------------|

| \$C060  | R7        | BIT 7=1; 40/80<br>switch set to 40<br>position |

| -       |           | BIT 7=0; 40/80<br>switch set to 80<br>position |

| \$C061  | R7        | BIT 7=1; Apressed                              |

| \$C062  | R7        | BIT 7=1;▲pressed                               |

## 4.2 Speaker

| Address | Operation | Function                                    |

|---------|-----------|---------------------------------------------|

| \$C03X  | R         | Speaker toggles<br>when this is<br>accessed |

Table 4-5 Sound control hardware location

A speaker is built-in. Sound of different tones will be generated depending on the rate \$C03X is being accessed. The loudness of the speaker can be adjusted by the volume control. The user can also use the ear-phone jack if he doesn't want to use the internal speaker.

## CHAPTER 5 THE VIDEO DISPLAY

## 5. THE VIDEO DISPLAY

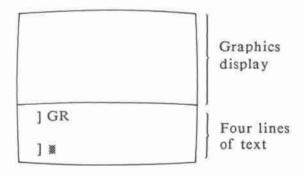

Besides conventional text display, the computer is also capable of displaying highresolution color graphics. The following is a brief summary of the features of the video display:

- 40-column x 24-row text

- 80-column x 24-row text

- 40H x 24V, 16-color low-resolution graphics

- 80H x 24V, 16-color double-lowresolution graphics

- 280H x 192V, 6-color high-resolution graphics

- 560H x 192V, 16-color double-highresolution graphics

- Mixed text/graphics display

- · Secondary display page

The video display is controlled by a number of "software-switches" resided in the hardware page described in chapter 3. Table 5-1 lists the locations and functions of the various video display control switches while Table 5-2 and 5-3 shows the switch settings for selecting the various video display modes and display pages.

| Address | Operation | Switch   | State | Function                               |

|---------|-----------|----------|-------|----------------------------------------|

| \$C000  | w         | INHPAGE2 | off   | Enable display<br>page 2               |

| \$C001  | w         | INHPAGE2 | on    | Inhibit display<br>page 2              |

| \$C00C  | w         | DBLRES   | off   | Select normal resolution               |

| \$C00D  | w         | DBLRES   | on    | Select double resolution               |

| \$C00E  | w         | CHARSET2 | off   | Select character<br>set 1              |

| \$C00F  | w         | CHARSET2 | on    | Select character<br>set 2              |

| \$C050  | R/W       | TEXT     | off   | Select graphics<br>modes               |

| \$C051  | R/W       | TEXT     | on    | Select text modes                      |

| \$C052  | R/W       | MIX      | off   | Select non-mixed<br>graphics           |

| \$C053  | R/W       | MIX      | on    | Select mixed text/<br>graphics         |

| \$C054  | R/W       | DPAGE2   | off   | Select display<br>page 1               |

| \$C055  | R/W       | DPAGE2   | on    | Select display<br>page 2               |

| \$C056  | R/W       | HGR      | off   | Select low-<br>resolution graphics     |

| \$C057  | R/W       | HGR      | on    | Select high-<br>resolution graphics    |

| \$C05E  | R/W       | INHDRGR  | off   | enable double-<br>resolution graphics  |

| \$C05F  | R/W       | INHDRGR  | on    | Inhibit double-<br>resolution graphics |

## Table 5-1 Video display control switches I/O locations

٠

#### THE VIDEO DISPLAY

| Display mode               | Control sy | vitch set | ting |     | -       |

|----------------------------|------------|-----------|------|-----|---------|

|                            | DBLRES     | TEXT      | MIX  | HGR | INHDRGR |

| 40-column text             | off        | on        |      | •   | 2       |

| 80-column text             | on         | on        | - 14 | ÷   | . v     |

| Low-res graphics           | off        | off       | off  | off |         |

|                            | × .        | off       | off  | off | on      |

| Db1-low-res graphics       | on         | off       | off  | off | off     |

| Hi-res graphics            | off        | off       | off  | ол  |         |

|                            |            | off       | off  | on  | on      |

| Db1-hi-res graphics        | on         | off       | off  | on  | off     |

| Low-res/40-column text     | off        | off       | on   | off |         |

| Low-res/80-column text     | on         | off       | on   | off | on      |

| Db1-low-res/80-column text | on         | off       | on   | off | off     |

| Hi-res/40-column text      | off        | off       | on   | on  | ¥.      |

| Hi-res/80-column text      | on         | off       | on   | on  | on      |

| Db1-hi-res/80-column text  | ön         | off       | on   | on  | off     |

Table 5-2 Selection of video display mode

|              | Control sw | itch setting |

|--------------|------------|--------------|

| Display page | DPAGE2     | INHPAGE2     |

| 1            | off        | -            |

|              | -          | on           |

| 2            | on         | off          |

Table 5-3 Selection of display page

The video display of the computer is memory-mapped, i.e. part of the system main memory is reserved for video display Each of the video memory purposes. "mapped" to a locations is particular drawing position on the screen. Depending on the video display mode, the resolution display, and color of the memory memory mapping requirement. and interpretation of video memory data may be different. These will be described in detail in the following sections.

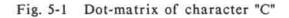

#### 5.1 Text modes

Text modes are selected by turning the "TEXT" switch on. In both the 40-column and 80-column text mode, the screen can display 24 rows of text. Each of the characters occupies a 7H x 8V dot-matrix on the screen. Except for some special characters, most of the characters are actually made up of a 5H x 7V dot-matrix, leaving a blank dot column at both sides and a blank dot row at the bottom of the character. Figure 5-1 shows the dot-matrix of the character "C".

#### 5.1.1 Character sets

The characters that can be displayed in the text modes include:

- Uppercase and lowercase letters

- Numerals

- Punctuation marks

- Special characters

An unique 8-bit character code is assigned to each of the displayable characters. The low-order six bits are simply the ASCII code for the character while the two high-order bits select one of three character display formats:

- Normal (white character on a black background)

- Inverse (black character on a white background)

- Flashing (alternating between normal and inverse format)

The computer has two character sets selected by the "CHARSET2" switch.

When "CHARSET2" switch is off, the primary character set is displayed. Uppercase letters, numerals and punctuation marks can be displayed in all three formats while lowercase letters and some special characters can only be displayed in normal format. The primary character set and the corresponding character codes are shown in Table 5-4.

|      |     | INVE     | RSE      |      |      | FLASH | ING  |      |        |        |     | ORMA | L.   |      |     |     |

|------|-----|----------|----------|------|------|-------|------|------|--------|--------|-----|------|------|------|-----|-----|

|      | 500 | \$10     | \$20     | \$30 | \$40 | \$50  | \$60 | \$70 | \$80   | \$90   | SAD | \$80 | SCO  | \$00 | SEQ | SFØ |

| ·SØ  | (i) | P        |          | 0    | 6    | P     |      | 0    | æ      | P      |     | Ø    | e    | P    | 29  | Ρ.  |

| -\$1 | A   | O.       | 11-      | 1    | A    | 0     | 1    | 31 1 | A      | 0      | - C | 8    | A    | 0    |     | 9   |

| -52  | 8   | <b>书</b> | 44       | 2    | Ð    | R     | -10  | 2    | 8      | FA.    | 10. | 2    | 8    | R    | tr. | 1   |

| +53  | c   | 5        |          | 3    | C    | 5     |      | 1    | C      | S<br>T |     | 3    | C    | S    |     | £., |

| -54  | Ø   | T        | 5        | 4    | D    | 7     | s    | 4    | D      |        | \$  | 4    | D    | т    | d   | 1   |

| 1\$5 | 8   | ω.       | <b>%</b> | 5    | E    | U     | 76   | 5    | E<br>F | U      |     | 5    | E    | U    |     | 14  |

| \$6  | F   | V        | 8        | 6    | F    | V     | 8    | 6    | F      | V      | 8   | 6    | F    | V    | i.  |     |

| \$7  | G   | w        | 1        | 7    | G    | w     |      | 7    | G      | w      | 1   | 7    | G    | w    | 9   | w   |

| +\$8 | H   | x        | 28       | 8    | H    | ×     | ×.   | 8    | H      | ×      | 0   | 8    | ++   | ×    | h   | *   |

| +\$9 | 1   | Y        | 1        | 9    |      | Y     | 0    | 9    | 1      | N.     | E.  | 9    | . T. | Y    | 0   | ×   |

| +\$A | 2   | Z        |          | 11.1 | 3    | Z     |      | 11 I | J.     | 2      |     |      | -1 C | Z    | 1   | 2   |

| -58  | ĸ   | 1        |          | 1.1  | ĸ    | F     |      | 3    | *      | 1      | *:  | \$1  | к    | î.   | k - | 13  |

| +SC  | L   | N        |          | - 1  | 1    | Ac    | 30   | 8    | Ł.     | 8      |     | 5    | L    | 1    | 01  | 10  |

| +50  | 1.1 | 1        | -        |      | м    | 1     | 27   |      | n/i    | 1      | -   |      | M    | 1    | m   | 1   |

| SE.  | N   | ×        |          | S    | N    | 16    |      | 5    | N      | A      |     | × .  | 14   | - K  |     | ~   |

| \$F  | 0   |          | 11       | 2    | O    |       | 1    | 2    | 0      |        | .27 | 2    | 0    |      | 13  |     |

Table 5-4 Primary character set

When "CHARSET2" switch is on, the secondary character set is displayed. Flashing format is not available for this character set but lowercase letters can now be displayed in inverse format. Moreover, some special characters (called mouse characters) can be displayed. Table 5-5 shows the secondary character set and the corresponding character codes.

|      |       | INVE | RSE  |             | MO     | JSE      | INVE | RSE    |      |      |          | NORM   | AL   |      |      |      |

|------|-------|------|------|-------------|--------|----------|------|--------|------|------|----------|--------|------|------|------|------|

|      | 500   | \$10 | \$20 | \$30        | \$40   | \$50     | \$60 | \$70   | \$80 | \$90 | \$AØ     | \$80   | \$CØ | \$DØ | \$EØ | SFO  |

| +\$0 | ø     | P    |      | 8           |        | 2        | τ.   | Ð      |      | P    |          | ø      | 0    | P    | 8    | Р    |

| +\$1 | A     | Ω    | 7    | 3 C 1       | Ā      | +        |      |        | A    | 0    | 1        | - E    | A    | Q    |      | 9    |

| +\$2 | B     | R    | 174  | 2           |        | *        |      |        | B    | R    | - 10     | 2      | B    | R    | b    | 10   |

| +\$3 | C     | S    |      | 3           | X      | -        | Φ.   | 3      | C    | s    |          | 3      | С    | 5    | C.   | 3    |

| +\$4 | D     | т    | \$   | 4           | 2      | 1        | 4    | × 1    | D    | T    | \$       | .4     | D    | т    | đ    | t    |

| +\$5 | E     | U    | 5    | 5           | $\sim$ | ->       |      | u I    | E    | U    | <b>N</b> | 5      | E    | 6.2  | 8    | ù.   |

| +\$6 | F     | v    | 8    | 6           | d      | *        | +    | × 1    | F    | V    | 8        | 5<br>6 | F    | V    | 1    |      |

| +\$7 | G     | w    | 1    | 5<br>6<br>7 | Trube  | <b>W</b> | g    | w      | G    | W    | 1        | 7      | G    | W    | g    | w    |

| +\$8 | H     | ×    | 1    | 8           | ÷      | ~        | . 61 | ×      | 14   | ×    | 1        | 8      | H    | ×    | b.   | . A. |

| +\$9 | 1 - E | Y    | 1    | 9           | -      | 5        |      | ¥      | 1    | Y    | 1        | 9      | ¥    | Y    | ¥1   | Y    |

| +SA  | 10    | z    | ٠    | Ξ.          | 1      | T        | 4    | z      | 3    | z    | 14       | Ē.     | 3.   | z    | £.   | 1    |

| +\$8 | K     | 1    |      | -           | *      |          | k    | 11 - I | ĸ    | T.   | 0#1      | 11     | ĸ    | T.   | ĸ    | 1    |

| +SC  | L.    | 1    | P    | <:          | -      | -        | E .  | 1      | 1    | 1    | 10       | ×.     | ī.   | 1    | 40   | 1    |

| +SD  | M     | 12   |      | 20          | 1      | 표        | 177  | î.     | M    | E    | -        | e      | M    | 1    | m :  | i -  |

| +SE  | N     | 1    | 1    | 3           |        | -        | n    |        | 74   | ~    |          | 2      | N    | A    | n    | ~    |

| +\$F | 0     | -    | 1    | 2           | ÷.     | T        | Ċ,   |        | 0    | -    | 1        | 7      | 0    | -    | 0    | *    |

Table 5-5 Secondary character set

## 5.1.2 Memory mapping

In both of the text modes, each character position on the screen is mapped to an unique location in the system memory. To display a specific character at a particular position on the screen, you only need to store the character code for the character to be displayed in the memory location which is mapped to the desired character position on the screen.

### 5.1.2.1 40-column text

40-column text mode is selected by turning the "DBLRES" switch off. In this mode, the screen is divided into 40 x 24 character positions. The 40 characters in a row are stored in contiguous memory locations called a row buffer. However, the row buffers for adjacent rows on the screen are not adjacent in the system memory.

The primary 40-column text page occupies locations \$0400 to \$07FF while the secondary page occupies locations \$0800 to \$0BFF of the main bank system memory. The memory mapping is illustrated in Fig. 5-2. THE VIDEO DISPLAY

| Base ad | dress    |           |           | Offset |      |          |

|---------|----------|-----------|-----------|--------|------|----------|

| Page 1  | Page 2 S | \$00 \$27 | \$28 \$4F | \$50   | \$77 | \$78 \$7 |

| \$0400  | \$0800   | Row 0     | Row 8     | Row    | 16   | Reserved |

| \$0480  | \$0880   | Row 1     | Row 9     | Row    | 17   | Reserved |

| \$0500  | \$0900   | Row 2     | Row 10    | Row    | 18   | Reserved |

| \$0580  | \$0980   | Row 3     | Row 11    | Row    | 19   | Reserved |

| \$0600  | \$0A00   | Row 4     | Row 12    | Row    | 20   | Reserved |

| \$0680  | \$0A80   | Row 5     | Row 13    | Row    | 21   | Reserved |

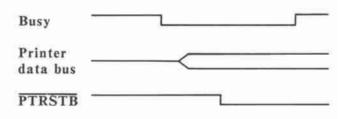

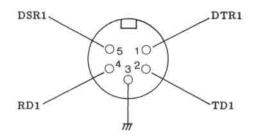

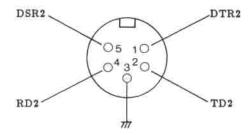

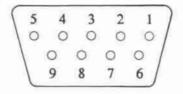

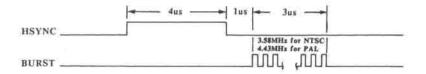

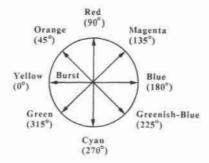

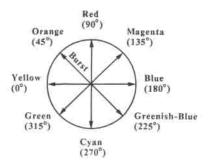

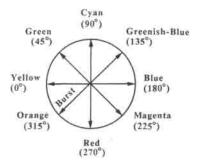

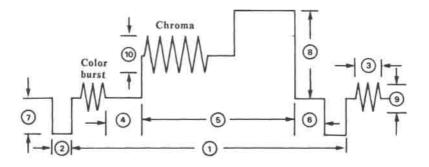

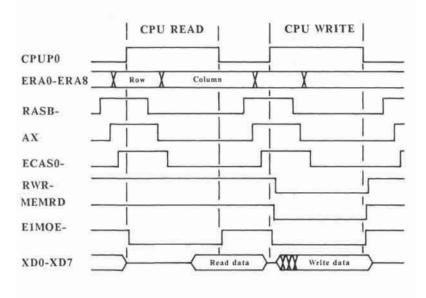

| \$0700  | \$0B00   | Row 6     | Row 14    | Row    | 22   | Reserved |